## LEARNING MATERIAL ON ANALOG ELECTRONICS & OPAMP

#### **DEPARTMENT OF ELECTRICAL ENGINEERING**

#### GOVERNMENT POLYTECHNIC KORAPUT

#### PREPARED BY: S BICHIBALLI

LECTURER IN ELECTRONICS & TELECOMMUNICATION ENGINEERING

pentovalent

(3 valence e)

elements

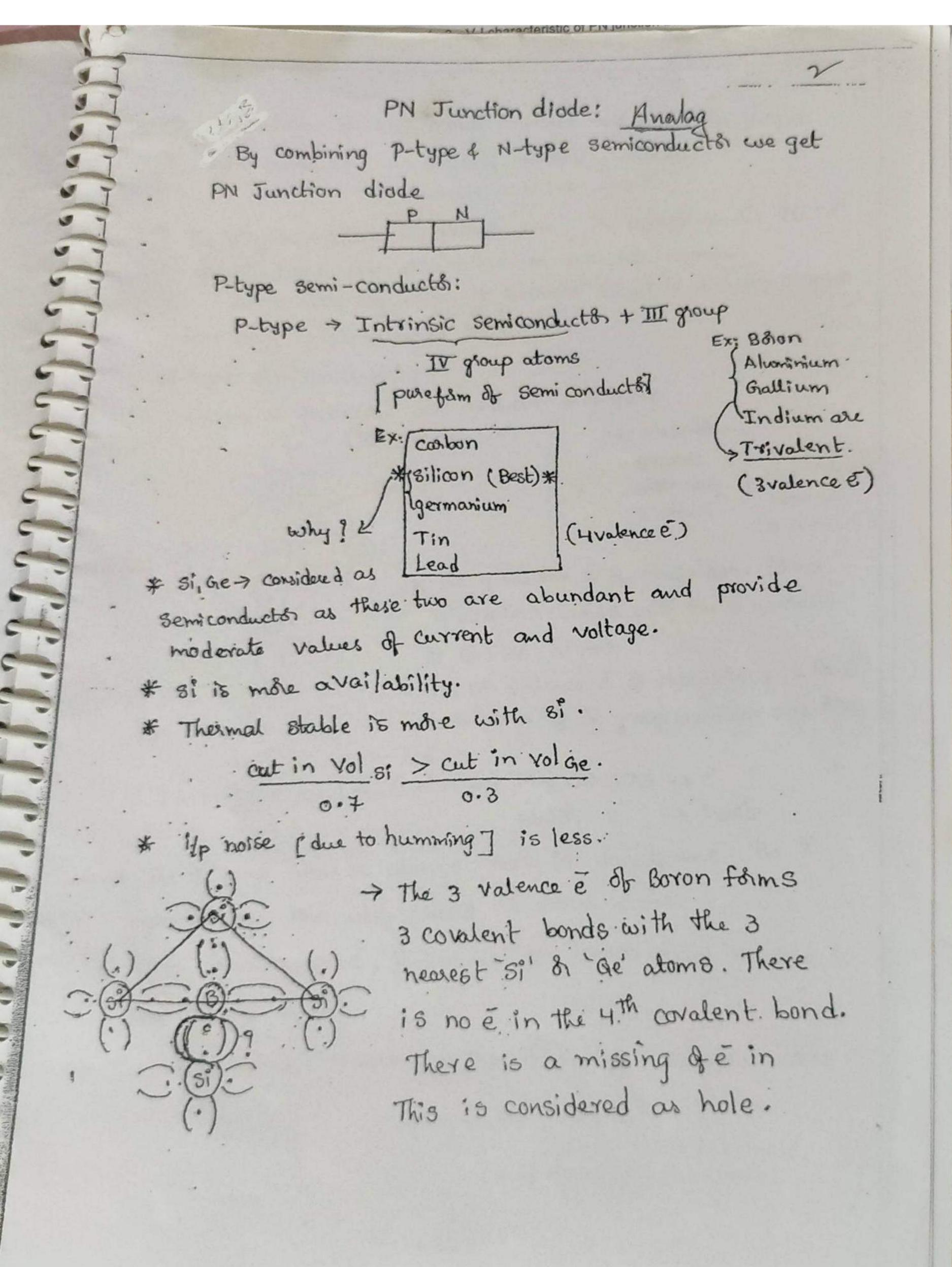

→ each atom of 3rd group provides one hole. In p-type semi conductor -> Majority corries -> holes minority corries -> ē

The 3rd group atom is always ready to accept an é. The 3rd group atoms are also called as Acceptor atoms.

After accepting an é, it becomes negative ion (81) acceptor ion and is represented by  $\Theta$ .

N-type semi conducto:-

N-type -> Intrinsic semi conductor + I group

(IV group atoms) Ex. phosphorous,

Arsenic

Antimony

Bismuth

\* The 4 valence e of phospholous forms

4 covalent bonds with the 4 nearest

3° (8) Gie atoms.

\* The 5th valence e of phospholous is free each atom of I group provides one free

\* In N-type semi conductor -> Maj carriers -> e Maj carriers -> e Moles.

\* The 5th group atom is always ready to donate an e- The I group atoms are also called as ponas atoms.

\* After donating one, it becomes the ion(d) donation and is represented by A.

The layer which separates p-type & N-type semiconductors is called Junction. Doping levels 1:108 > Intrinsic

Doped atoms atoms.

> P-type & N-types are equally doped.

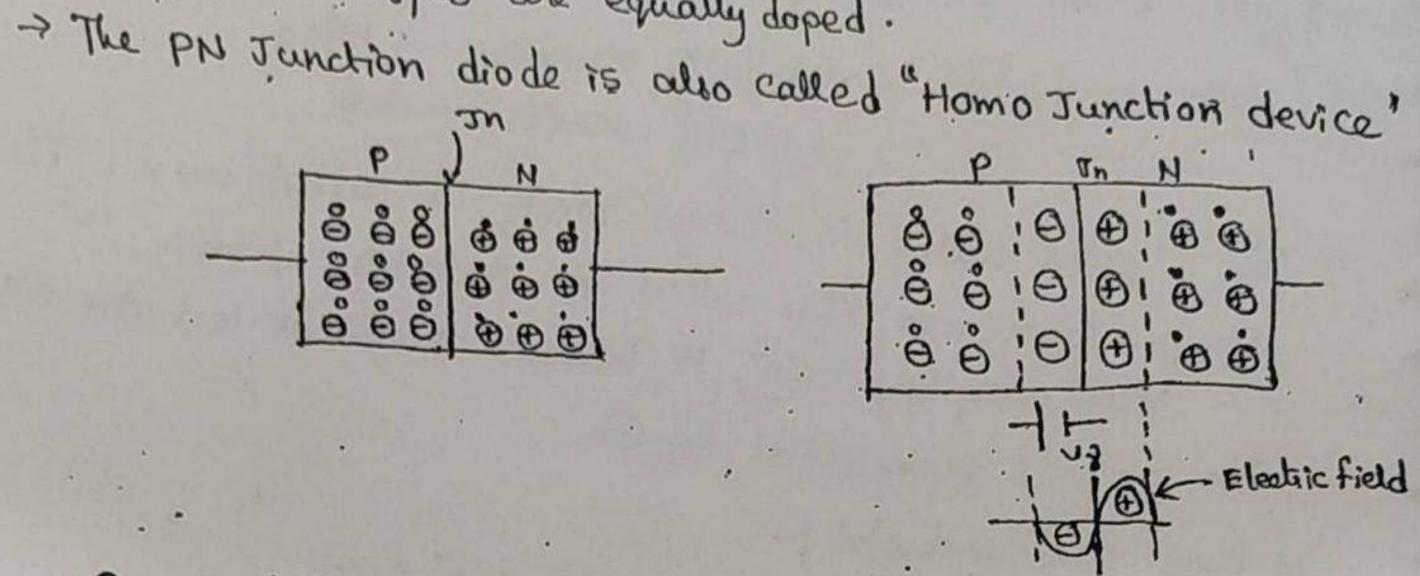

acting on the Tunction. This force causes motion in the charged posticles, these charged posticles from higher concentration to lower concentration is elections moves from N-side to P-side & holes moves from p-side to N-side. Due to this recombination takes place in both the regions as p-type & N-type are equally doped, the recombination rate is some in both the regions. The depletion region width is same in P-type & N-type regions. The depletion in which there is no cavailability of charged posticles is called depletion region.

The induced voitage across the Junction is called depletion region voltage (d) space charge region voltage (d) cut in voltage (V).

$V_T$  - Temperature dependent voltage  $V_T = \frac{KT}{9} = \frac{T}{11,600}$

At Room temp, T= 300°K VT = 300 ~ 26mV.

The applied voltage across the diode in such a way that, that makes the conduction of current in the direction of arrow head is called forward biasing.

Reverse bias of PN Junction diade:-

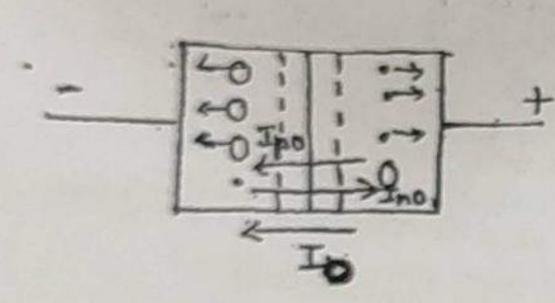

\* All the majority corriers are moving away from Junction. They cannot from [loop | Imajority = 0]

\* The mindity courses moves towards the Junction.

AS-R-B voltage 1:-

\* The majority carries move rapidly attracted by their respective commend voltages i.e more rapidly move away from Junction.

-> Depletion region width 1.

- Junction resistance 1.

. -> Junction temp 1.

AS YM, bire Dep. region width M.

Temp across Junction M, Hence

Temp across Junction M.

The mindity corriers crossing the Junction M.

ASTA, Breakge of covalent Bond?

ē-hole pairs are generalised 1, Hence

of the no. of mindity courriers crossing the Jun 1.

Ino = Ino + Ipo

This Is flows from N-type to p-type to reverse to the direction of arrow head 'I'm Reverse current.

The Reverse current at Room temperature is called reverse Saturation current.

As VMM, TMM, IOM

At some particular voltage, temp across the Tunction becomes max. This temp permanently damages the PM Junction drode.

This voltage is called "BREAK DOWN VOLTAGE" (\$2300).

AS T1, Io1

As every ic rise in temp Io1 by 7%.

for every 10°c.1 in temp, Io Doubles

T20 - T60

T02=T01 2 (T2-T1)

1. T02=T01 2 (T2-T1)

Tic -> To

characteristics:-

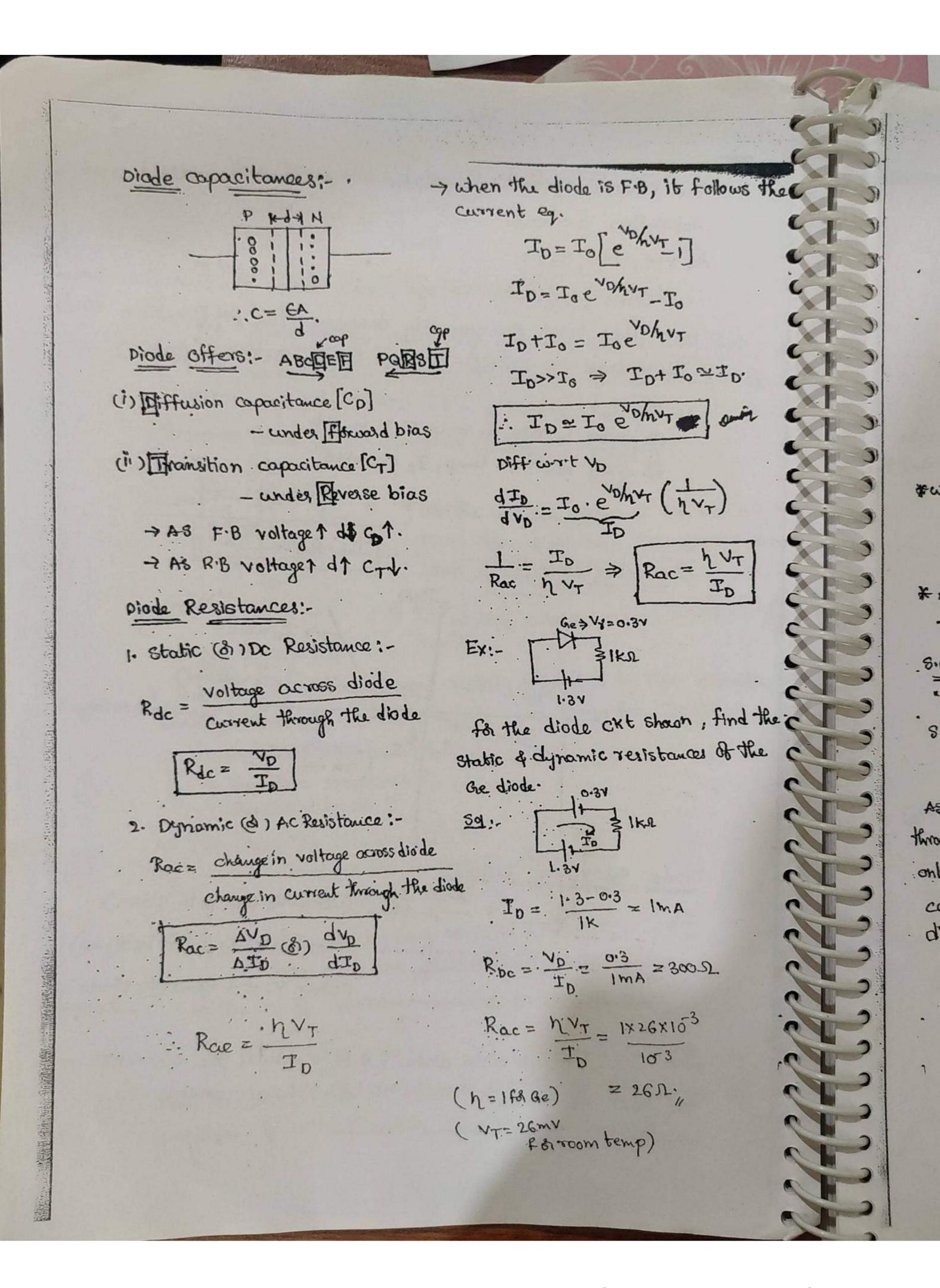

To=To[e -1]

VBD

Vth (knee Voltage)

VTh reshold voltage)

To (UA -> Ge)

NA -> Si)

Diode equivalent <u>circuit</u>:

\$\frac{1}{2} \text{Rf} \text{Cwhen V\_8 & Rf both given}\$

\$\frac{1}{2} \text{ML.} \text{Cwhen only V\_8 given in Rf=0}\$

\$\frac{1}{2} \text{Cwhen V\_8=0 & Rf=0 (&) Diode is } \text{DEAL}\$

R.B - H \* when diode R.B it conducts the currents in the older of UA (Ge diode), hA (Si). These currents core insignificant.

# O.C & S.C Tests Poi diode Ckts:

### O.C. Test: -

"All the diodes are replaced by

\* calculate (VA-Vc) for each diode

\*when no-of diodes having (YA-Vc)>Vz,

the diode which has more (VA-Vc) becomes ON First.

\* Again calculate (VA-Vc) For remaining diodes.

#### .S.C Test:-

"All the diodes are replaced by 8.c" PN C > ->--

Assume the current directions through each diode from PtoN type only.

calculate the current through each diode:

# problems:

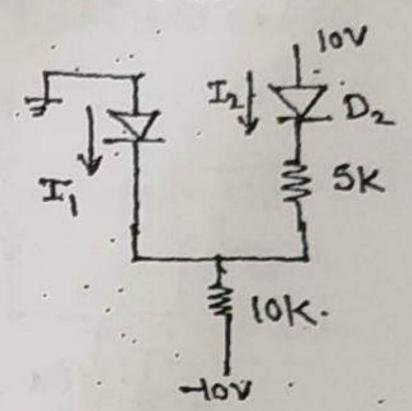

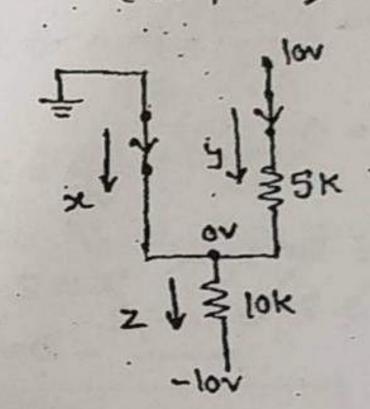

Pb:- For the diode ext shown, calculate the currents I, 4 Iz, assume that diodes are ideal

501: - (1) D, 4 D, ore replaced by soc

$$y = 10-10$$

$2mA$

As  $y > 0 \Rightarrow D_2 - 0N$  (Assumption Correct).

$Z = 0+10 = 1mA$

$$Z = x + y \Rightarrow x = Z - y$$

$$= 1mA - 2mA$$

$$= -1mA.$$

# Applications of Diodes:-

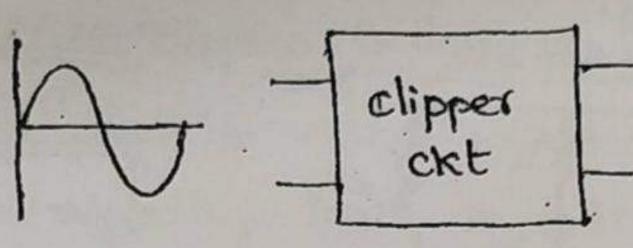

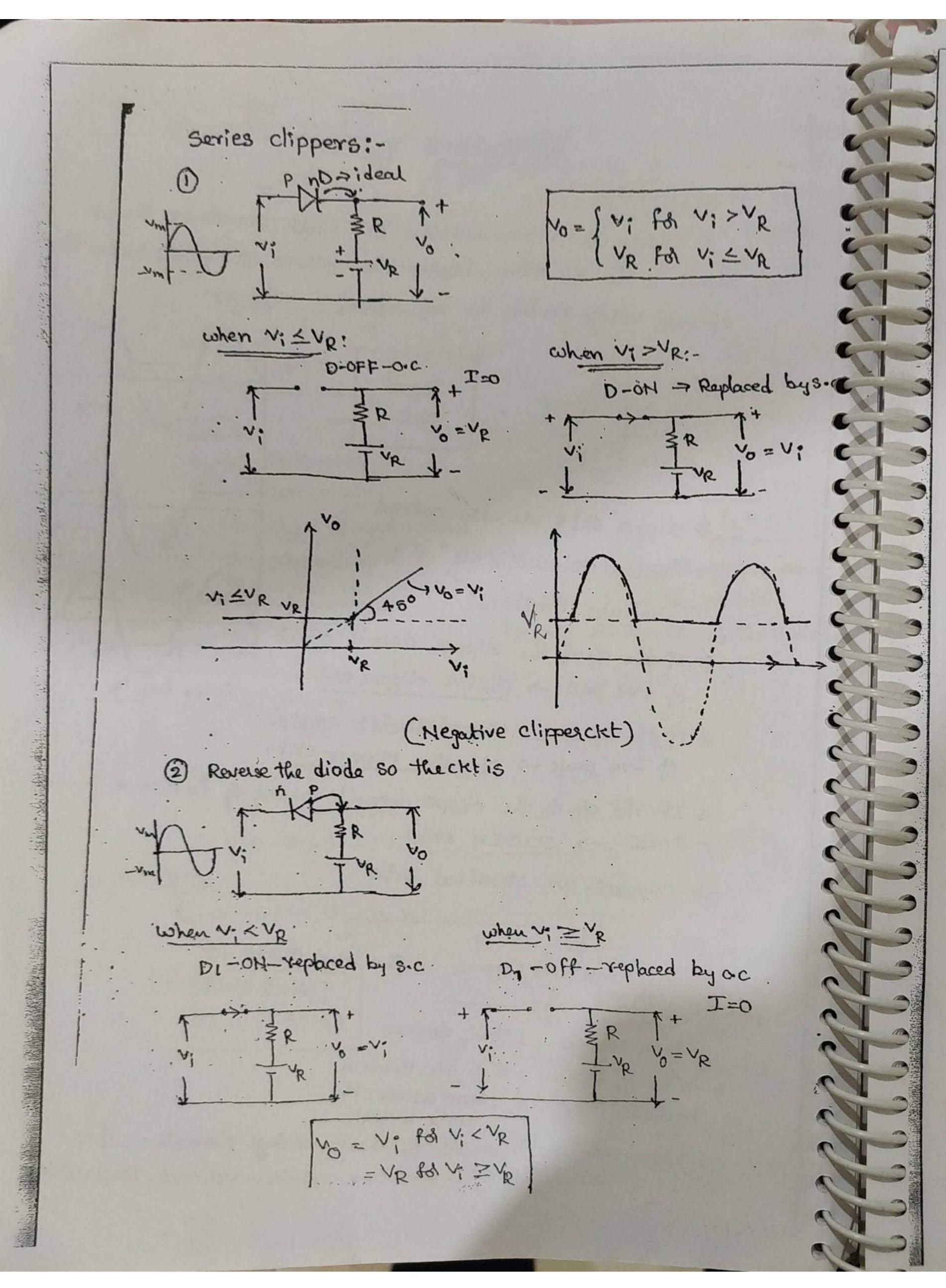

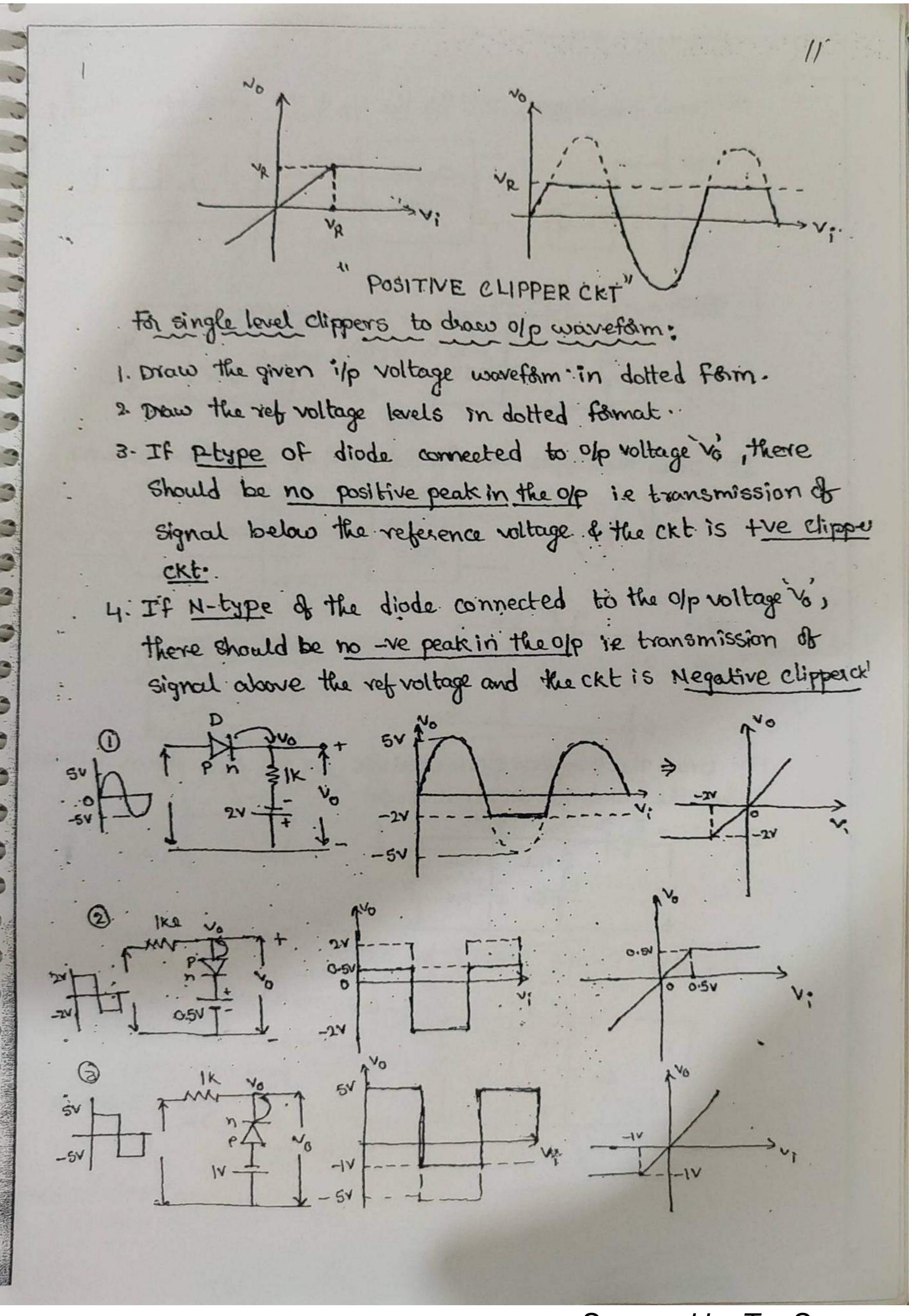

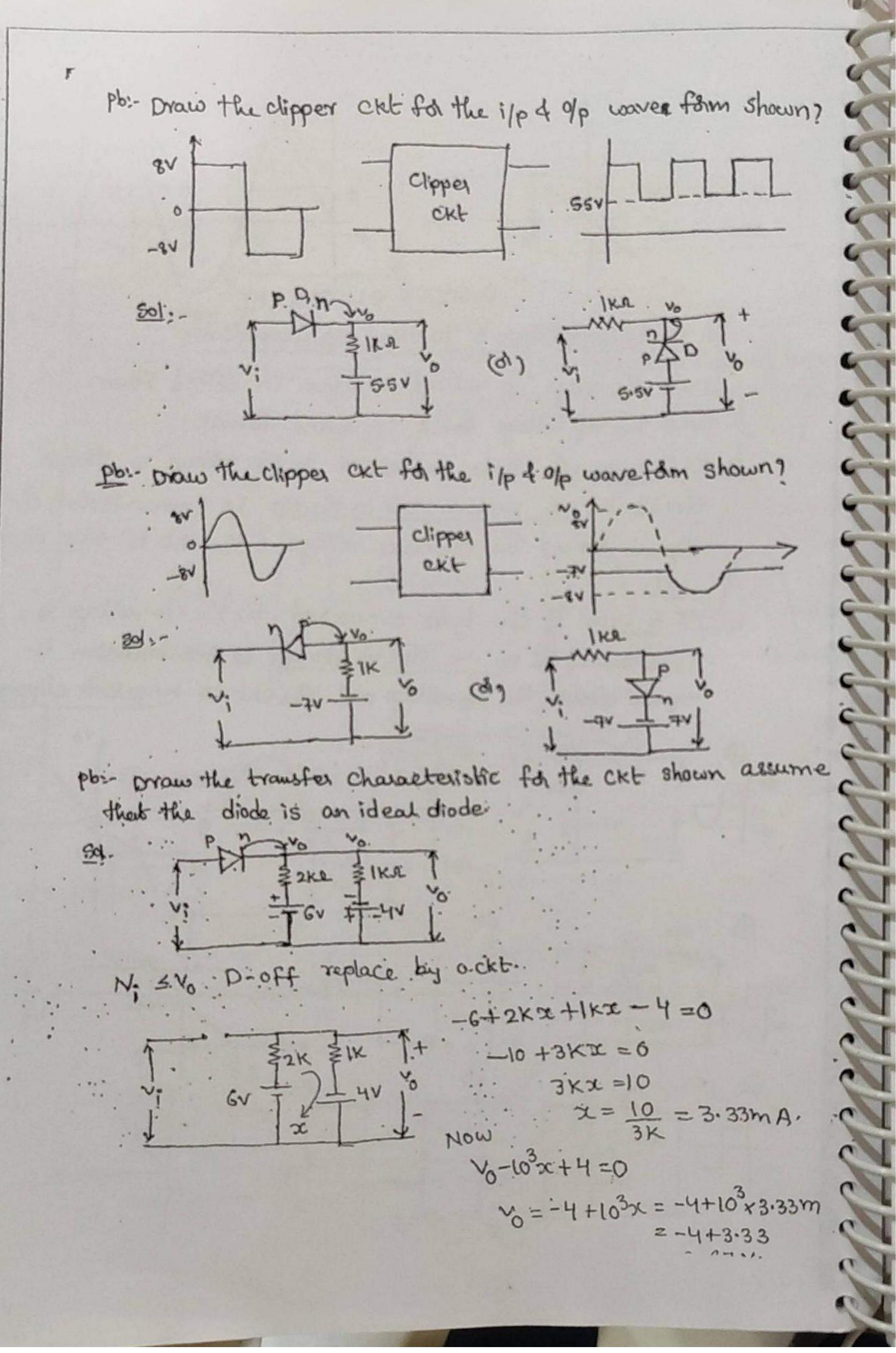

### 1. CLIPPERS: -

\* Clipper is a transmission ckt which transmits the ip signal to the olp either above the reference voltage (d) below the reference voltages.

\* clipper ckts are also called as "voltage selector ckts" (3).

"voltage limiters".

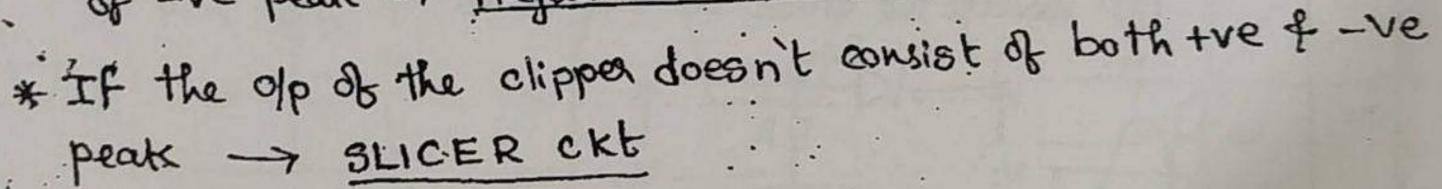

\* If the op of the clipper doesn't consist

of the peak -> positive clipper ckt

\* If the 9p of the clipper doesn't combist

of -ve peak -> Negative clipper ckt.

=> clippers are classified into

single level clippers. Two level dippers

[Sticer Ckts]

series clippers I shunt clippers

this i/p is given I \* In this, 9p taken

\* Inthis i/p is given 1 \* In this, 9p taken

to diode

to diode

Diode branch

-> clipper exts doesn't consists of energy stolage elements: L4.C.

NR

Scanned by TapScanner

Scanned by TapScanner

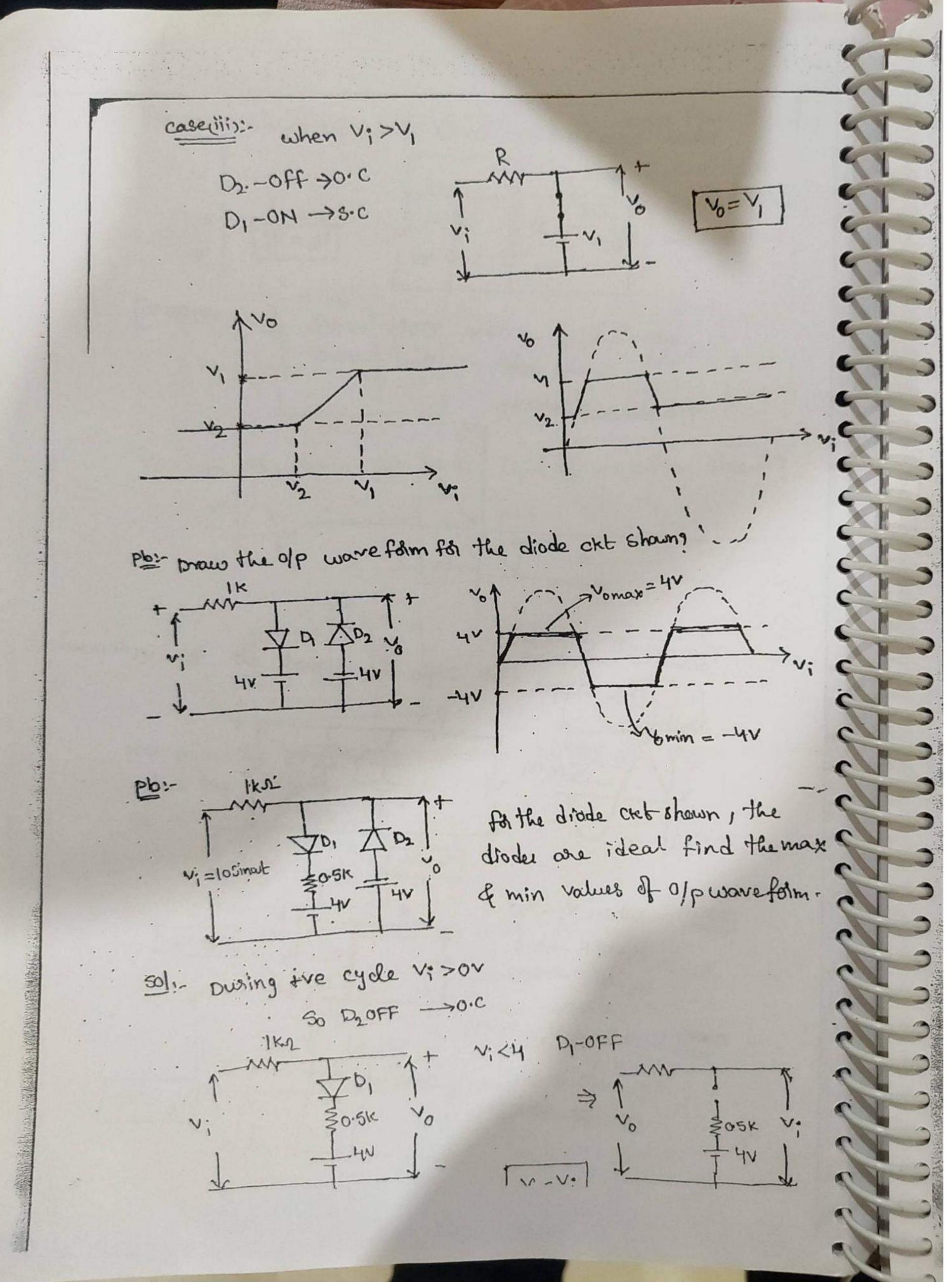

when v. > -0.674, D-OH > replaced by s.c. Doft -> o. C [vo= -0.67 v] when v: < -0.6.7 v DON ->S.C. V: > -0.67 V T/f characteristics:-This clipper ckt clips the signal at two independent Two level clippers:-Voltages casein: when vox V2 D1-0FF ->0.0 case(i). when  $V_2 \leq V_1 < V_1$ DI-OFF->0.C

Scanned by TapScanner

Scanned by TapScanner

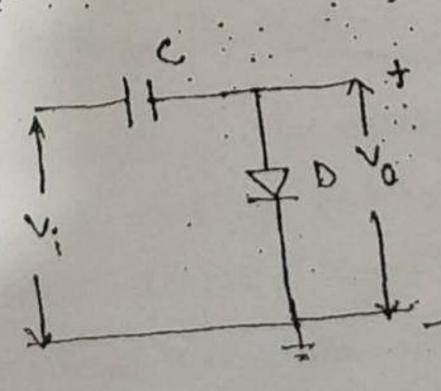

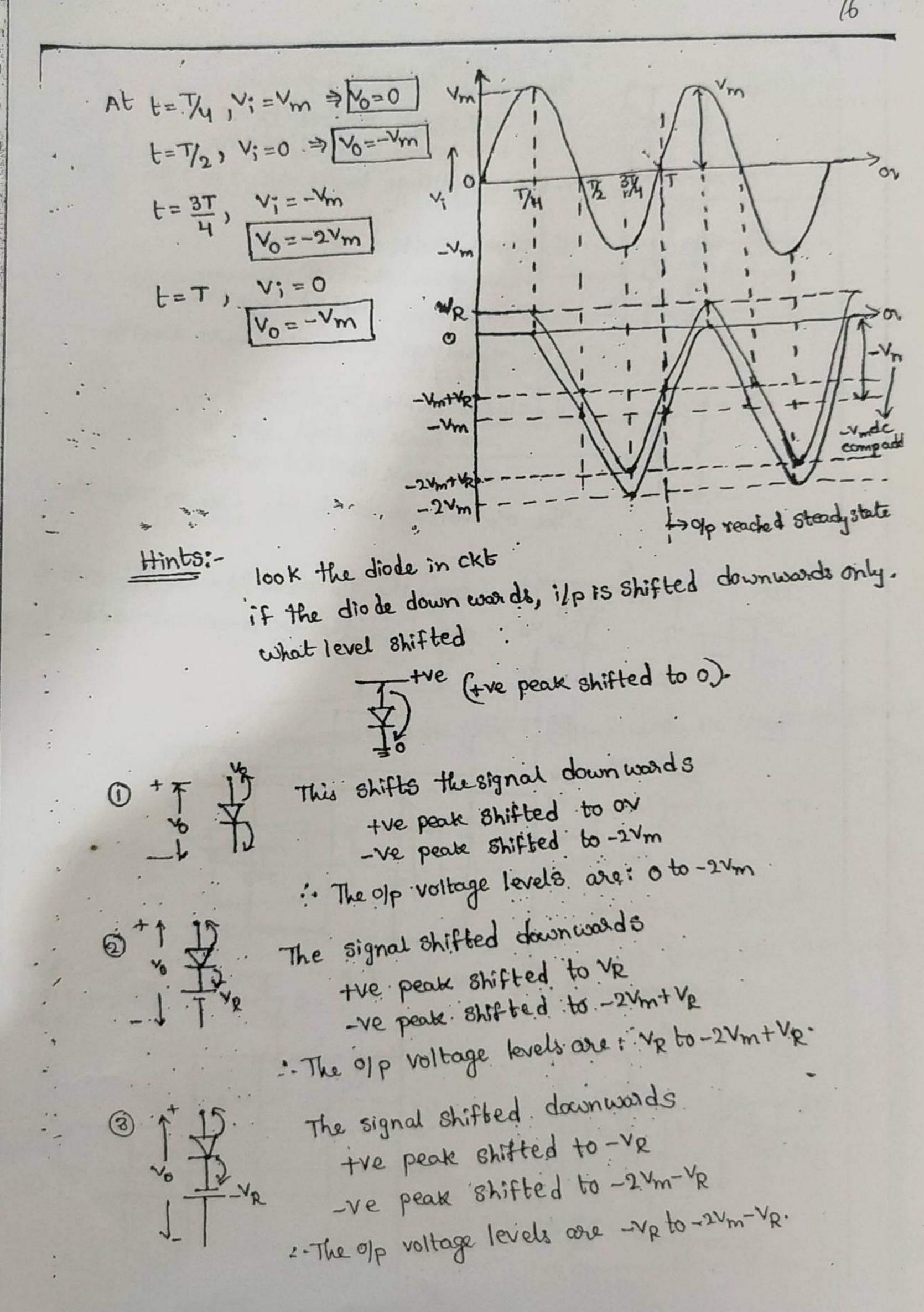

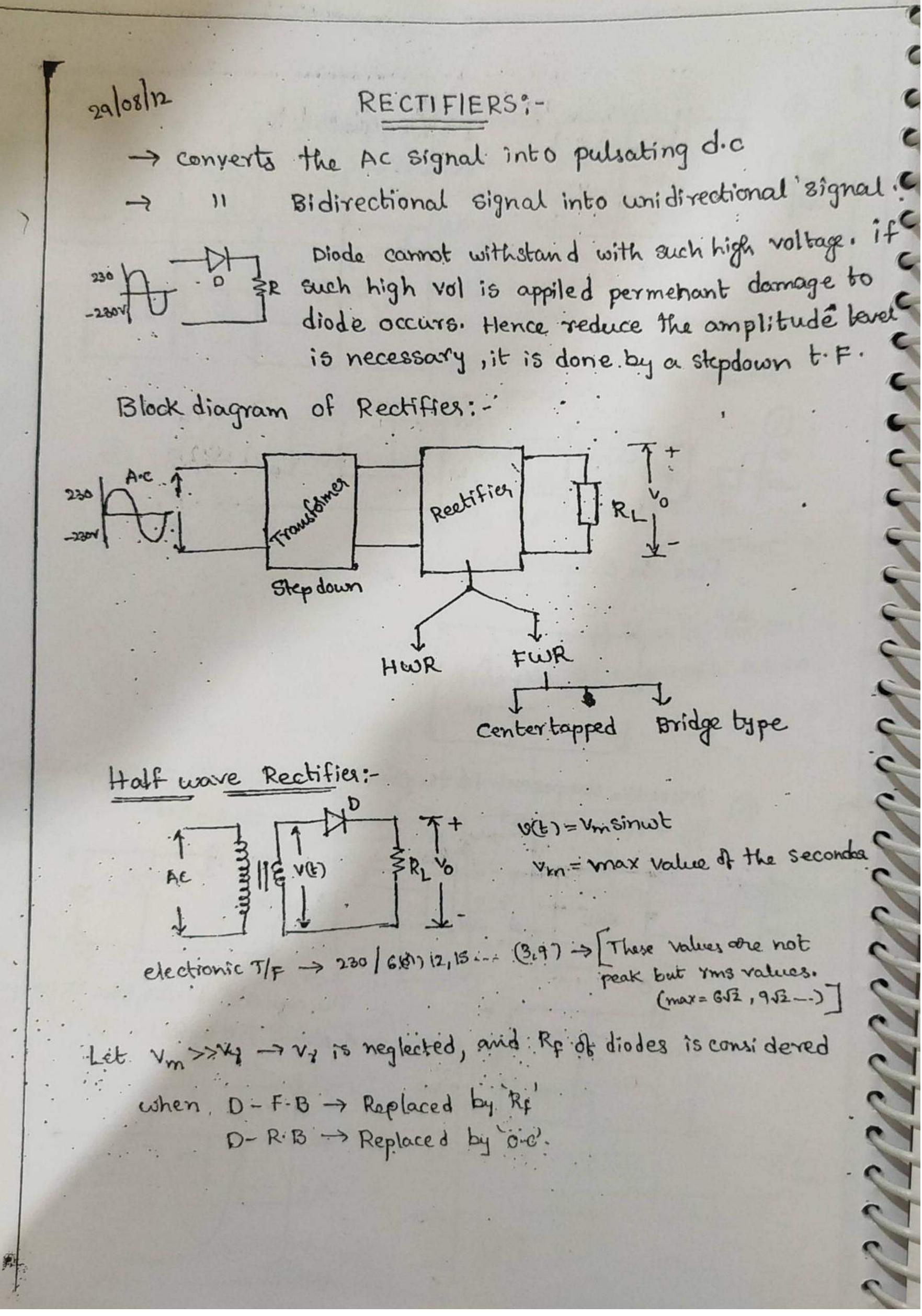

#### CLAMPERS:-

- > The clamper ckts are used to shift the signal either upwards

- appiled signal > positive clamper ext.

- → If the signal shifted downwords clamper inserts -ve do

→ Negative clamper ckt.

- -> clamper exts are also called as 'DC inserter ckts' (3)

Dc Rest der exts'

- -> All the restorer cuts are called inserters but not vice vers

- -> clamper ckts consists of energy stolage elements like c'or

[L-Bulk, cost so 2 > not prefe

- > Input signal always given to capacitionce only.

- > In clamper

(VP-P)=(VP-P);/p

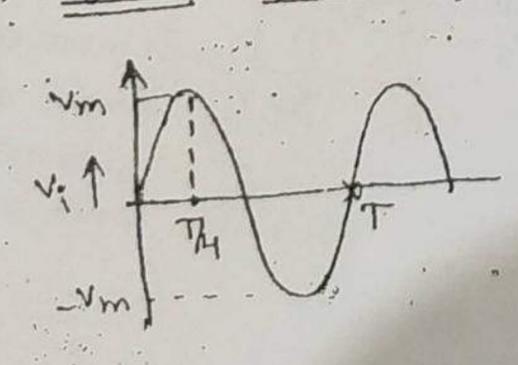

The analysis of a damper chet always starts with the conduction of diode . Megative clamping.

clampers classified into 2 types <

1 +ve clamping.

-ve clamping ext also called as the peak clamper ext the clamping ext also called as the peak clamper ext

1. Negative clamping ckt:

Let assume that the capacités is initially eunchorged ie  $V_c = 0$  & diode is IDEAL { ON S.C. OFF O.C. when V; >0, DON -> s.c The capacitor charges in accordance with the 1/p voltage when t= 7/4; V;=Vm Vc = Vm (the coppacitos charges to the max Value of Vm). , Vc = Vm V; LVm (Just less than Vm) V; -Vc -Vo = 0 Vo = V; -Vc = < Vm - Vm vo = - ve voltage This negative voltage makes the diode off state D-off -> replaced by o.c. No discharge path for the capacités 30, capacités holds the prev voltage i.e Vc=Vm adcinsated in clamper introduce -Vm to applied v; hence -ve clamper

Scanned by TapScanner

To calculate 402 consider lower half bridge: VD2+ 16+VD3 = 0 402 = - [ No + ND3] = - [ VmRL + VmRf

2Rf+RL ] sinut = - Um CRL+Rf ) sinut VP\_ ~ - vmsInwt Similarly VD4 =-Vmsinwb (PIV) DRIDU = Ym During -ve cycle of V(E):-B -> tre -> D2-ON, D3-Off A -> -ve -> Dy-ON, D1-off Vo=Vmsinwt +BV VD2 = VD4 = Imsinwt Rf VD3 = VD1 = 9 -i(t) = Vm Sinwt = Instnut 2RftRL 10= 1(F) BT Vm RL shwt (2RC+R) Voz. Vinsinut RL>>Rf. To calculate ups consider lower half bridge. VD2+VO+ VD3 = 0 VD3 = - 16+ VD2 VD3 = VmRL + VmRf Sinwt ~ - VmSinwt. Similarly I ( DIV) n. n= Vm Vn = - Vmsinut.

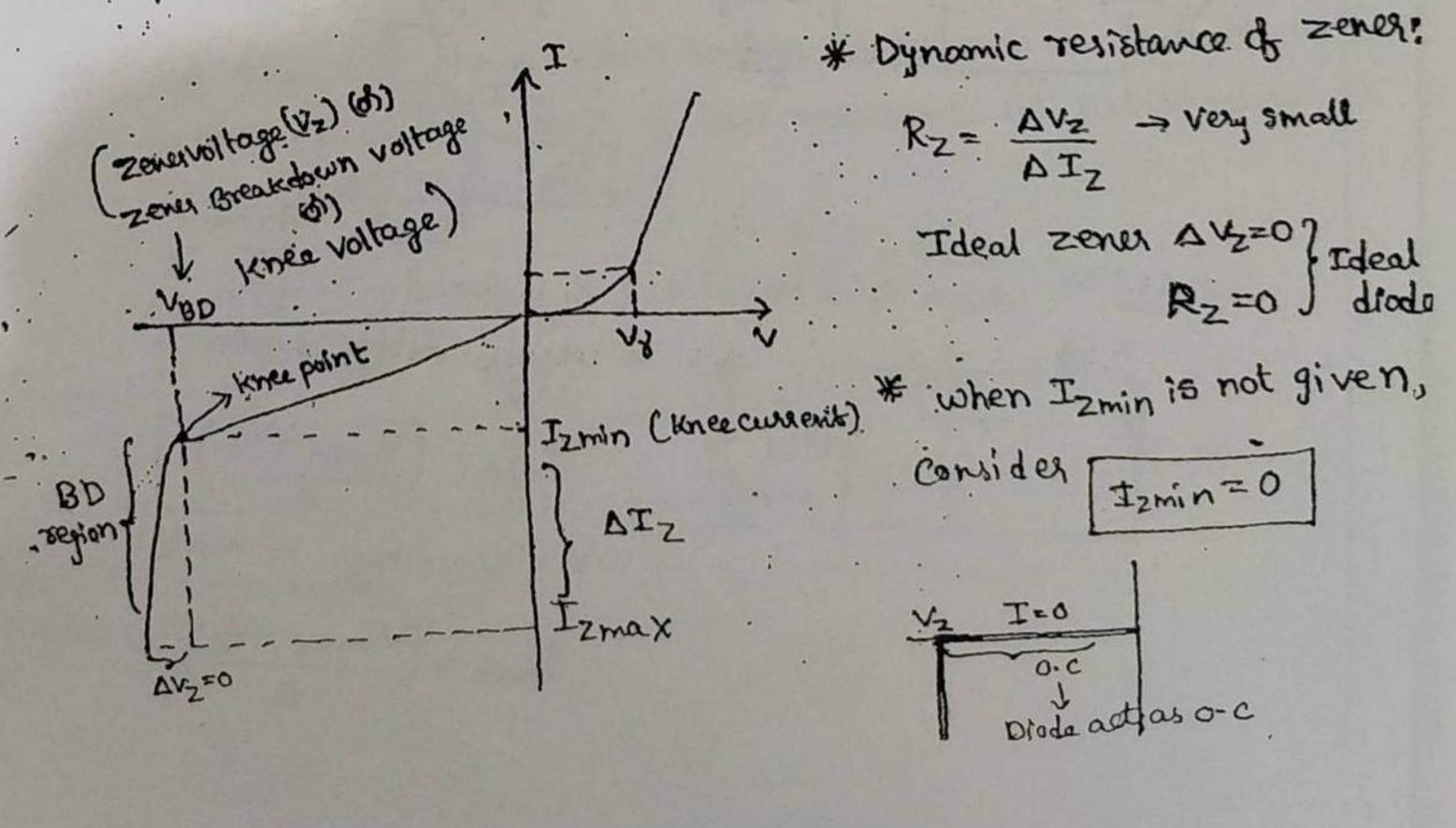

# Zener Diode Characteristics:-

### purpose: -

1. To operate in the reverse bias region.

To conduct the currents in the order of mA in R.B. region

2. To withstand for large generation of temperature.

Once breakdown occurs, uniform electric field across the

Tunction & it maintains constant voltage across its

terminals i.e acts as voltage Regulation.

3. The Break down voltage of Zener is less than that of PN Tunction diode. Tomax temp.

4. zener diade is heavily doped compared to PN Junction diad

Doping l'évels: 1:106

Toped atoms

doped atoms

5. zoner diodes are of silicon type only.

> A heavily doped si diode which has 8haap breakdown voltage is called zenes diode. When zenes diode is F-B → acts as normal PN Junction diode of 8i type.

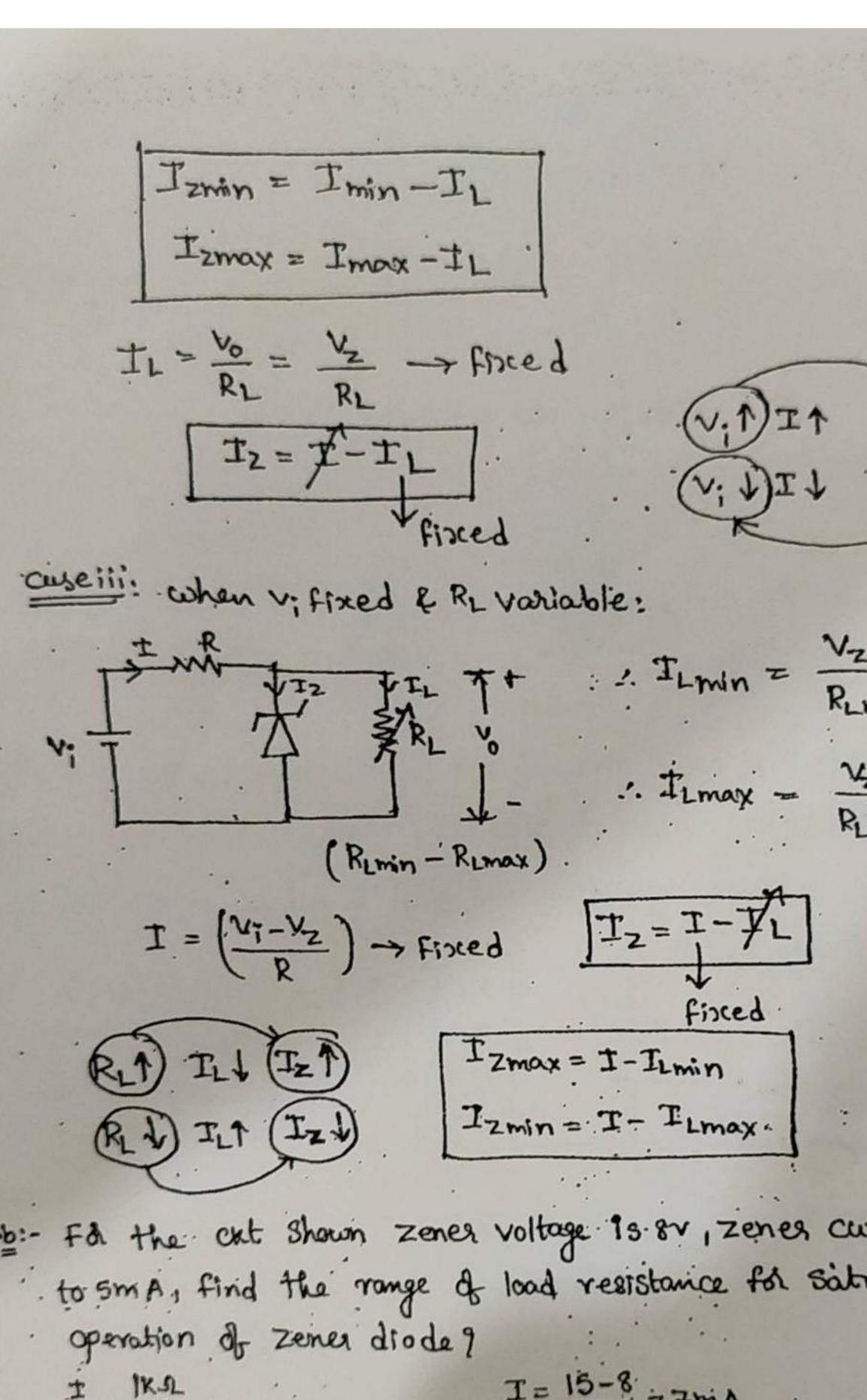

ner equivalent ckt:zoner diode as voltage Regulation:-Zenes. diode must. operate in the Breakdown region. A voltage regulation is a ckt which maintains constant voltage across its terminals even vi (8) Ri valies. Caseci): when Vi4RL are constant = IL= 1/2 -> Fixed I = (Vi-Vz) -> fixed casecisis when vi is variable & RLis fixed > when ip voltage is min Imax = (Vimax - 1/2)

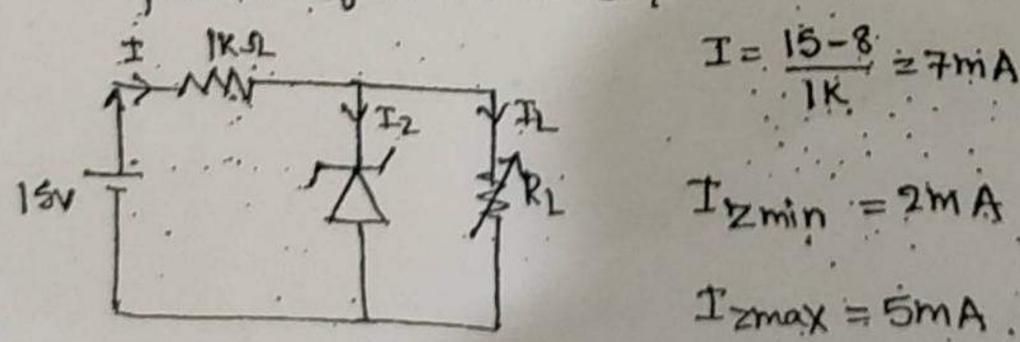

pb:- For the cut shown zoner voltage 15.8v, zoner currents are 2mA to 5 m A, find the range of load resistance for Satisfactory

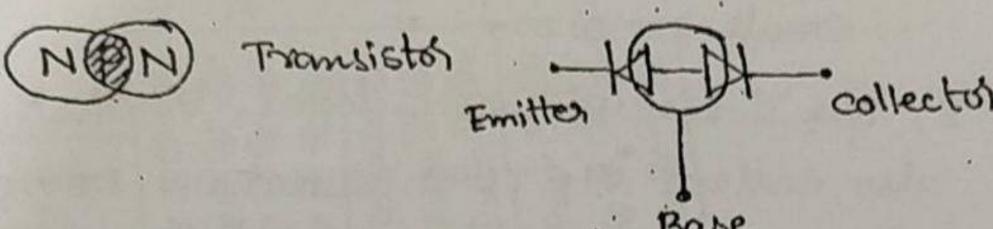

## TRANSIS TOR :-

\* Transistor Fundamentals:TRANS/ISTOR

Transfer of

Transfers the signal from one resistance level to another resistance level i-e signal transferred from i/p post to 0/p post.

-> while transfering the signal from ilp pat to oppost

it does the amplification process.

- > Depending on conduction of current due to charged particles (ē & holes) transistés are classified into:

- 1. Bipolas tromsistor

- 2. unipolar transistés.

=> Bipolas transistor:

- \* The current conduction due to both \( \varepsilon \) + to both \( \varepsilon \) + The current conduction due to both \( \varepsilon \) + A holes

- \* Depending on construction principle BIT classified into 1. NPN transistor

2-PNP transistor

The mobility of ē (Un) is greater than that of holes (Up) i.e Un > 2.6Up

- \* The conductivity in MPN transists is more than that in PNP transists.

- \* NPN transistors are preferably used compared to PNP.

- \* BJJ is a current controlled device. i.e the old current is controlled by the i/p current.

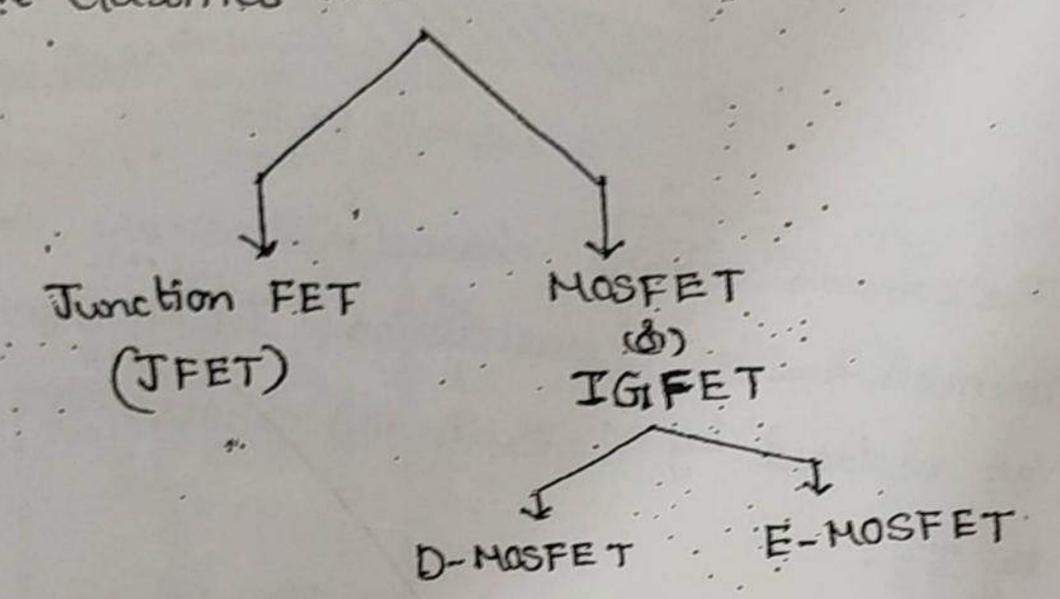

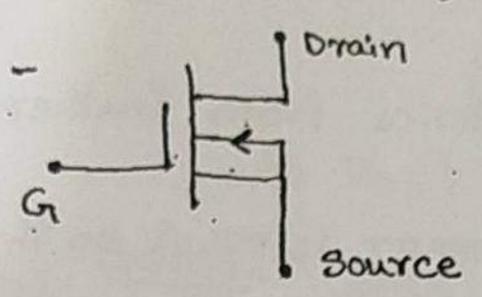

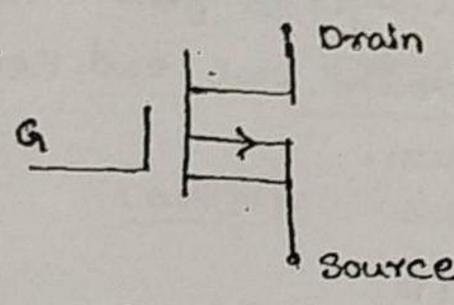

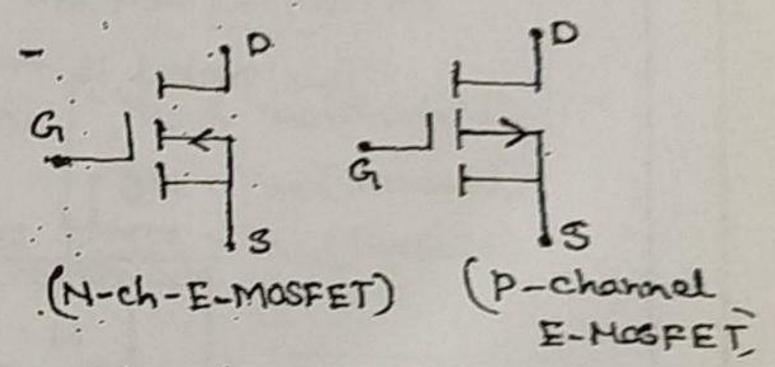

\* oppowerent depends on i/p current. . Opcurrent = fun [i/p current] > unipolar transistes:-\* The current conduction due to either ē à holes. \* The current conduction due to only e-Nichannel FET. The current conduction due to only holes - P channel FETC N channel FETS are preferably used compared to p channel FETS. · Depending on the construction principle FETS are classified into: · JFET 2. MOSFET (1) Insulated gate FET (IGFET) Depletion Enhancement MOSFET. MOSFET \* FET is a voltage controlled device. ie the opp current is controlled by the applied ilp voltage. ofpourrent = f. [i/p Voltage] \* FET is a Low Moise device compared to BJT.

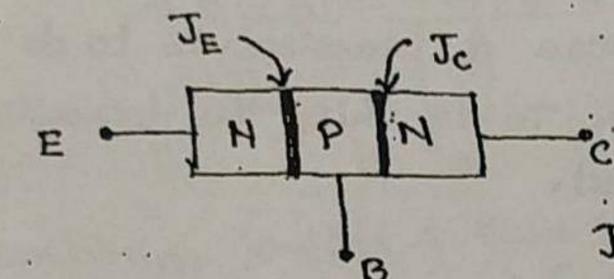

Bipolag Junction Transleto :- (BJT)

TE > Emitter-Base Junction

Jc > collect& - Base Junction (a) collect& Jun.

B W N E

PNP transister:-

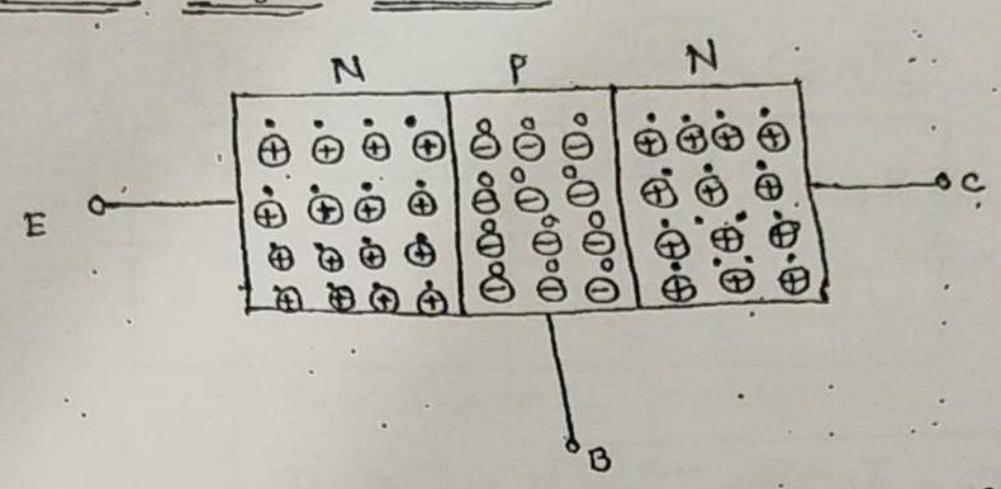

Emitter:- To emit the charged partieles.

- Heavily doped.

- . Medium in size.

collector: To collect the charge & particles which are emitted by emitter.

- Moderately doped.

- Large in size.

Base: To control the current through the transista - Lightly doped. - small in size. \* E', B'4'c' are uniqually doped. So that the BJT is also called "HETERO JUNCTION DEVICE" \* The main purpose of transister is to do the faithful amplification. To do this, the transistor must be properly biased. i.e JE-F.B ] -> Active Region. Region of Application Junctions operation OFF Switch . cutt off Region Jc - R·B J JE-F.B ]-> Amplifier. Active Region ON switch. JE-F.B J-> Saturation Attenuatos. Inverse Active region Creduce the amplification Transista never used in this region (Reason is this) 30 the transister will not do the Attenuated process. R2: R1=1:9 The Attenuate process will. done at low cost in this ckt (Resister)

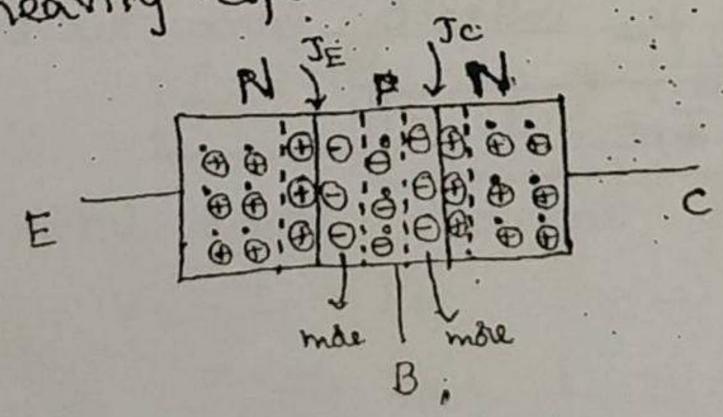

By combining emitter & Base a small force acting on the Tunction (JE) this force causes motion in the charged posticles, these charged posticles always charged posticles, these charged posticles always moves from higher concentration to lower concentration is the elections moves from n-type to p-type f holes moves from P-type to N-type to this recombination takes place in both the regions as emitter is heavily dobed compared to base the recommbination rate is mane in both side side compared to emitter side.

So that the depletion region width is more into Base side compared it to emitter side.

Similarly By combining collector of Base the deplection region width more into base side compared to collector side. Simply in the transists the deplection collector side. Simply in lightly doped side compared region width more into lightly doped side compared to heavily doped side.

Apply Kel in Edlector.

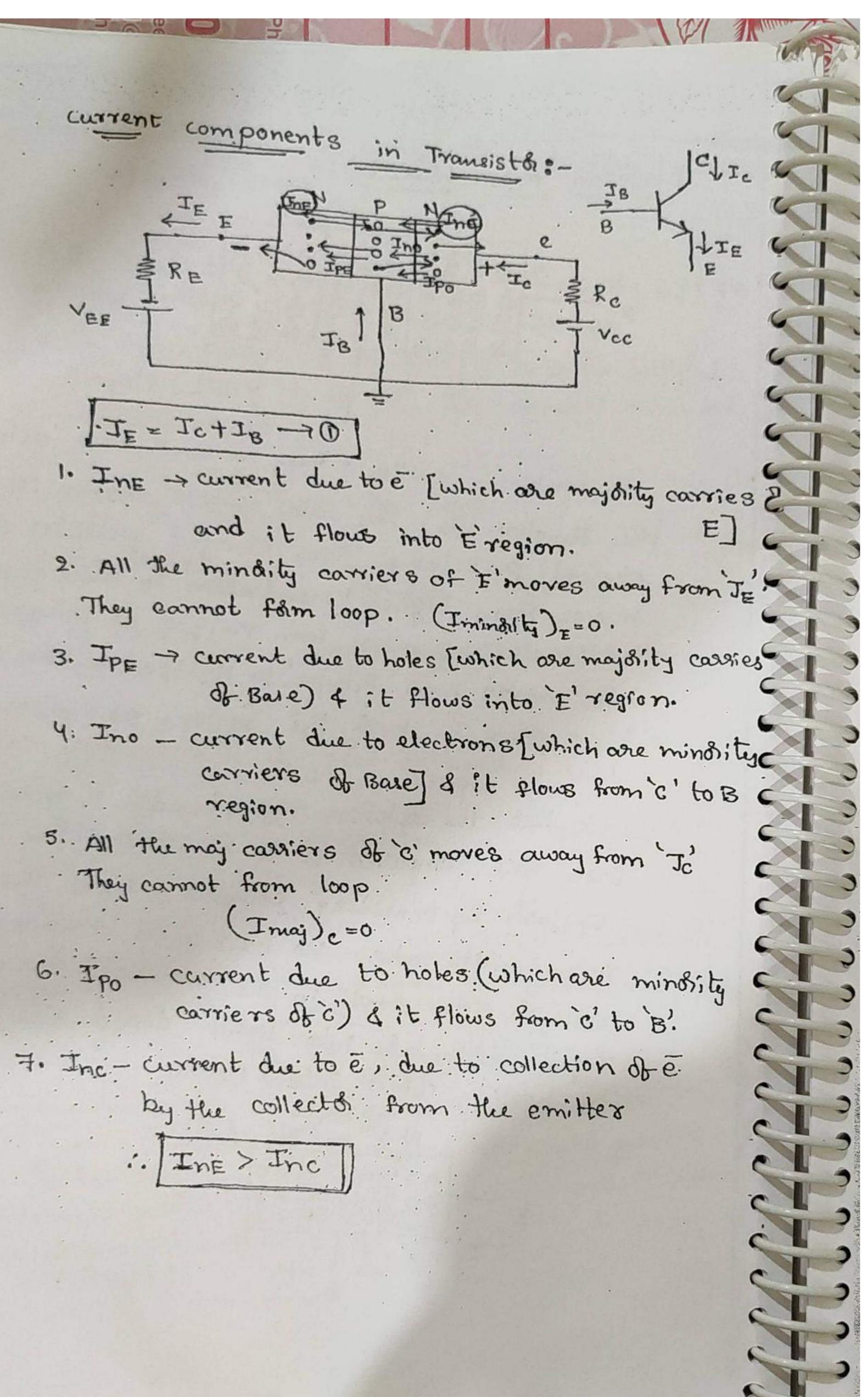

\* These 4 eg'n are called transistor Fundamental current equations.

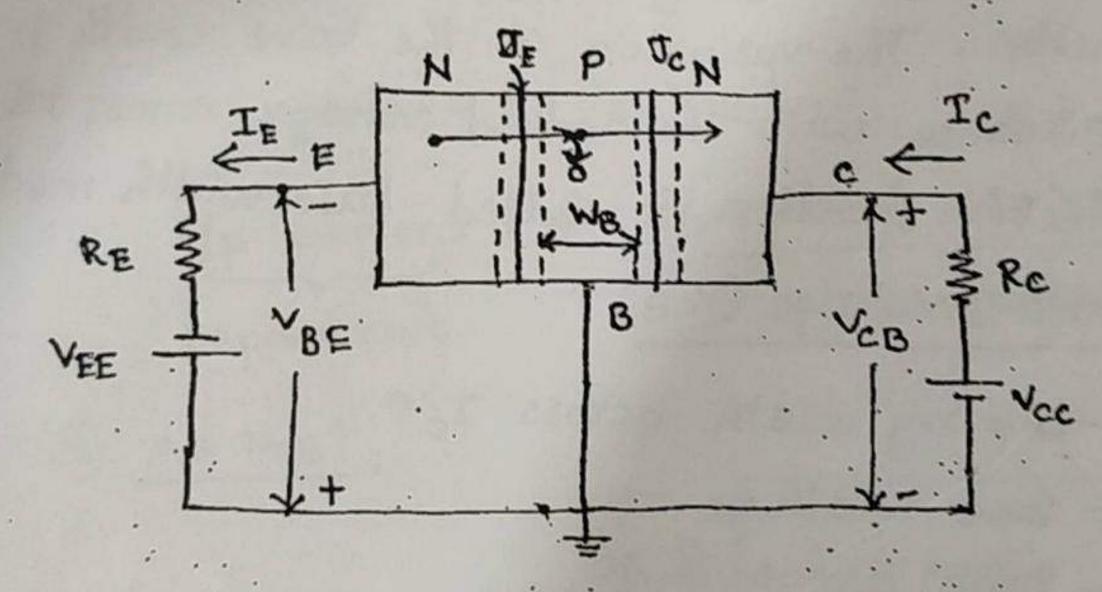

Common Base):-

The injected maj cassier current at c'

The total Emitter current

$$\mathcal{A} = \left(\frac{\mathcal{I}_{nc}}{\mathcal{I}_{E}}\right) (\delta) \frac{\mathcal{I}_{c} - \mathcal{I}_{o}}{\mathcal{I}_{E}} \qquad \mathcal{I}_{c} = \alpha \mathcal{I}_{E} + \mathcal{I}_{co}$$

Inc = & IE zd(Jc+IB)

-> The total collector current is

$$I_c = I_{nc} + I_o$$

=  $\alpha(I_c + I_B) + I_o$

->. The total emitter elarrent is

$$= \left(\frac{\alpha}{1-\alpha}+1\right) T_{B} + \frac{1}{1-\alpha} T_{0}$$

$$I_{E} = \frac{1}{1-\alpha} \left(T_{B}+T_{0}\right)$$

when  $T_{0}$  - Neglected;...

$$T_{nc} = I_{c}$$

$$\alpha = \frac{T_{c}}{T_{E}} \stackrel{(b)}{\otimes} \gamma \boxed{I_{c}} = \alpha T_{E}$$

$$T_{c} = \alpha \left(T_{c}+T_{B}\right)$$

$$T_{c} \left(1-\alpha\right) = \alpha T_{B}$$

$$T_{c} = \frac{\alpha}{1-\alpha} T_{B}$$

$$T_{e} = \frac{1}{1-\alpha} T_{B}$$

$$T_{e} = \frac{1}{1-\alpha} T_{B}$$

The relation blue  $\alpha + B : S_{1}$ :

$$\alpha = \frac{B}{1+\beta} \quad \beta = \frac{\alpha}{1-\alpha}$$

$$\alpha = \frac{1}{1-\alpha} = \frac{1}{1-\alpha} \left(T_{B}\right)$$

The collector current is

$$T_{c} = \frac{\alpha}{1-\alpha} T_{B} + \frac{1}{1-\alpha} T_{0}$$

$$T_{c} = \beta T_{B} + \frac{1}{1-\alpha} T_{0}$$

$$T_{e} = \frac{1}{1-\alpha} \left[T_{B} + T_{0}\right]$$

$$T_{e} = \frac{1}{1-\alpha} \left[T_{B} + T_{0}\right]$$

All the above equations valid for Active region of operation.

Base width Modulation: - (81) EARLY Effect: -

AS . VBE 1

- Depletion region width across JEI

- Base width 1.

VBE 17 Base width 11

\* when VBE = V8. Depletion region width of JE becomes

Zero.

AS VBE 1 (beyond Vr) - There is no variation in Base wildth.

AS VCB1

- Deptetion region width 1 (this 1 more into lightly doped region in Base)

- Base width 1

VCBTT Base width \$1

At some particular voltage VcB, the depletion region becomes max. 4 occupies the base region Base width = 0.

The collector Junction permanently damages.

\* The Base width modulation is related to the reverse bias voltage applied across the collector Tunction. The variation of the base width in aces dance with the applied voltage across the collector Junction is called base width modulation.

## > AS R.B voltage (VCB) 1

- Depreg width across Ict

- Base width &

- Temp across Jc 1.

- collectes able to collect more no of charged Particles. Ict

- Rate of recombination of ē holes pairs in the base 1.

1

S. K.

TI

THE

### consequences of BWH:-.

- O AS VCB 1

- Depletion reg. width across Ict

- Base width &

- Recombination. Rate in Base 1

- Ict

The value of It' depends on the value of VCB.

BIT is a current controlled device.

Ofp current = f [1/p current, olp voltage]

Dependent

Tradependents.

2 AS VCB1:-

- Temp across in Ict

E THE STATE OF C+

- Breakage of covalent Bondsp

- in c4 B.

- e hole pairs 1 in e 4 B.

- Inot, Ipot

- AS TOT ICT

- IPET AS IPET, IET

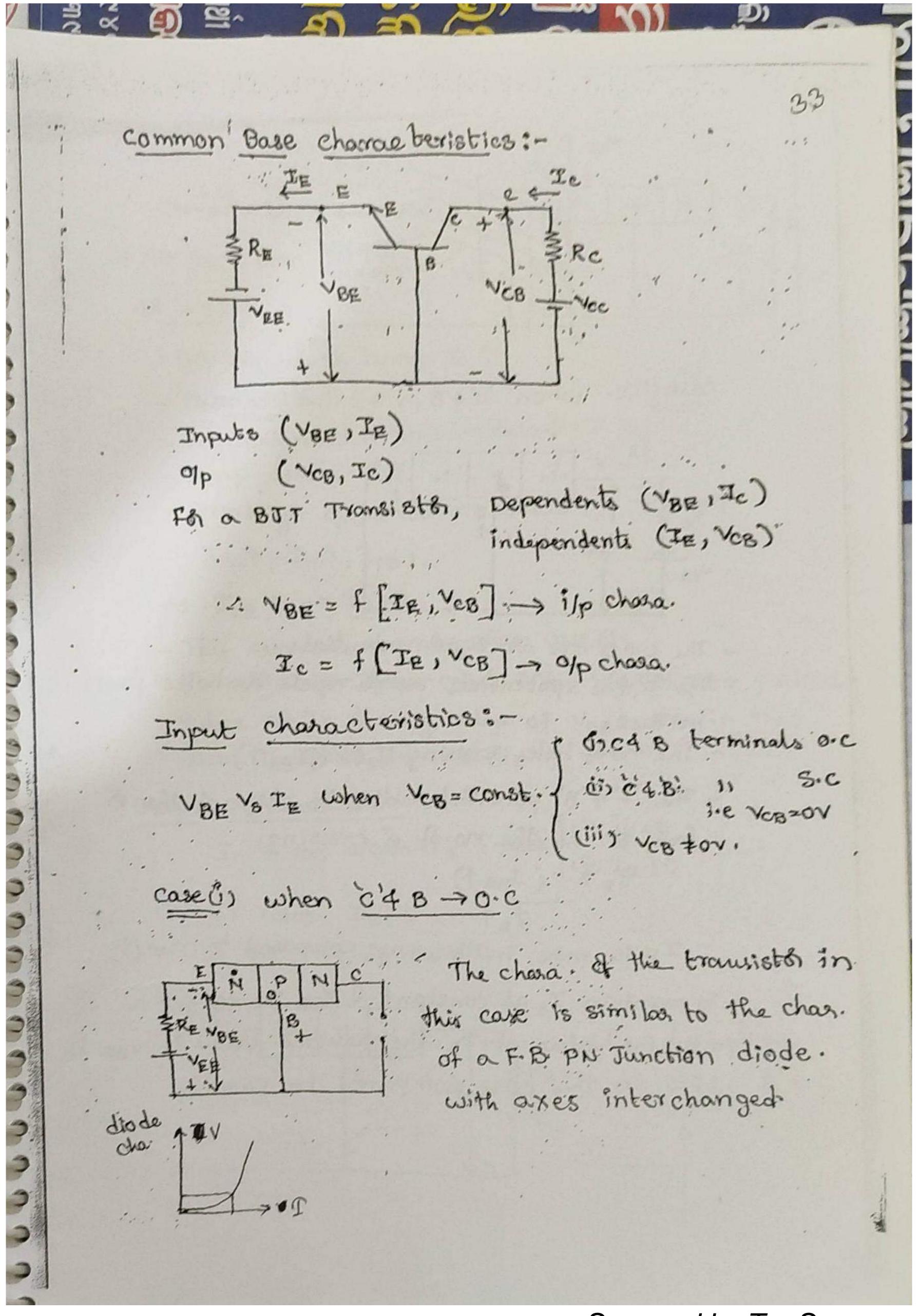

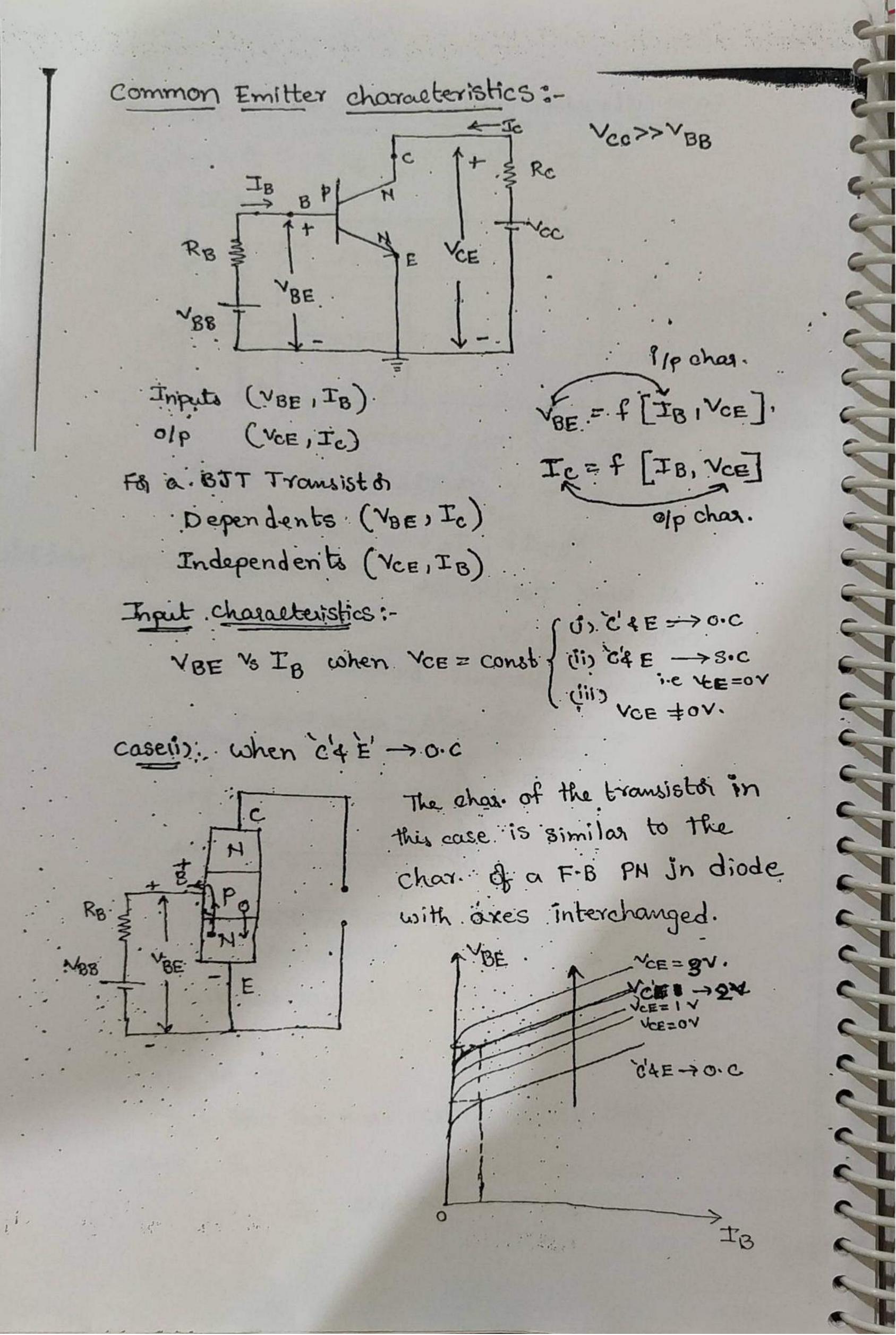

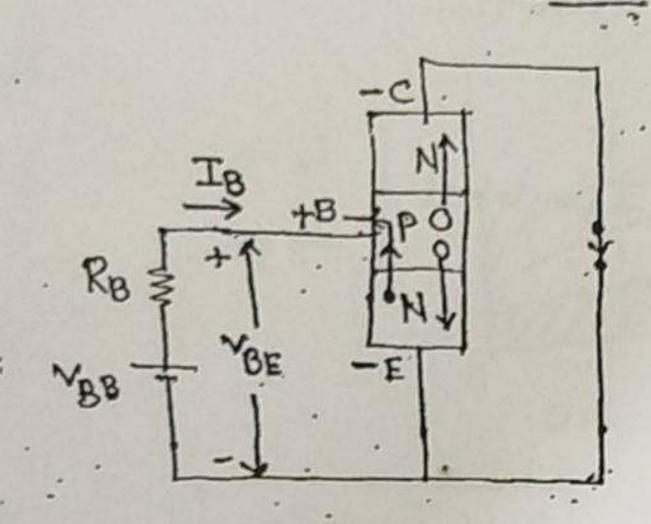

AS VCB 1 - IPT. To maintain IE at a constant level, & VBE. Dependingon the value of IE VBEL By comparing VBE & IE > VBE = f [IE] VBE & VCB > VBE = f [VCB] · · VBE = f [IE, VCB] Ilp voltage = f [i/p current, o/p voltage] \* foi a BJT transistor:-Indepentients (I/p current, 0/p voitage) Dependents (Ilp voitage, Opcurrent) Ilp charaeteristics:-I/p valtage vs i/p current when olp voltage = constant. I/p voltage (Dependent) 1/p current (independent) Ofp charaeteristics:-1.9p current oppoirment vs opprollage when ilp corrent = constant of p voltage

B -> 3.c (i-e ver=ov) case (ii): - when 'c'4B -> - The c48 acre at same potential. - The ic' & B' potentials repels the holes present in Base. - The no-of holes crossing JET (IPET) - The c'4 B' potentials adde to attract the E from E': so the no. of e crossing. JEA (INE 1) IE is more in this case compared to case (9) - To maintain I as constant & VBE i e to get a posticular value of IE. the required Value of VBE is LESS in this case compared to case (i).

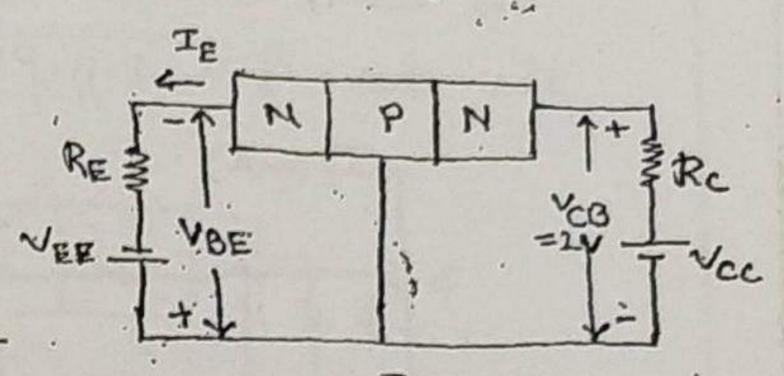

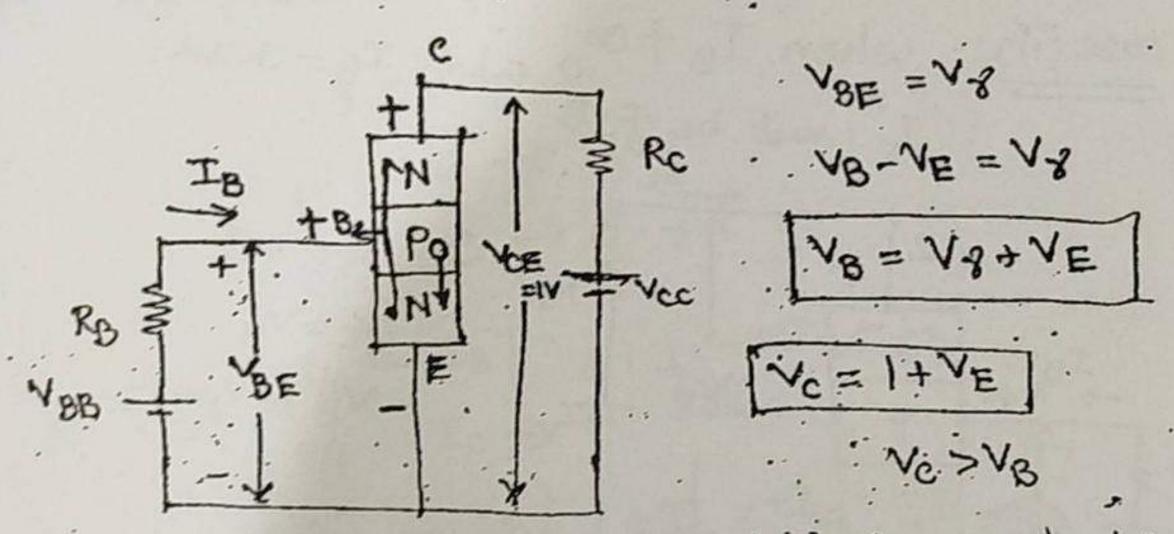

case (ili): - When VCB + ov

Let NOB = 2V.

\* AS VCB 1 from oto 2Y

AS YOBT

- Dep reg. width across Jc 1

- Base width t

- Recombination rate in Base of

- Temp across Jc 1

- Breakage of covalent bonds in c'4 BT

- Inot, Ipot, Ipe 1.

AS - TPE + -> TET -

- This current is more than case (i)

- To maintain IE as const: 4 VBE i.e To get a pastiadas Value of IE the req value of VBE is less in this case compared to case (15.

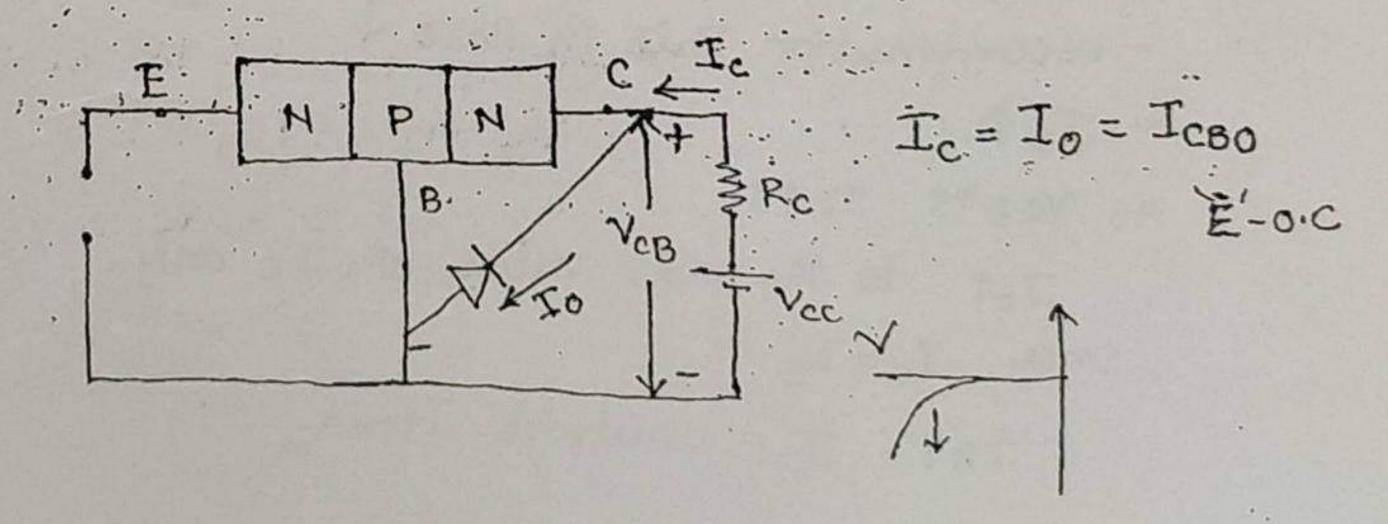

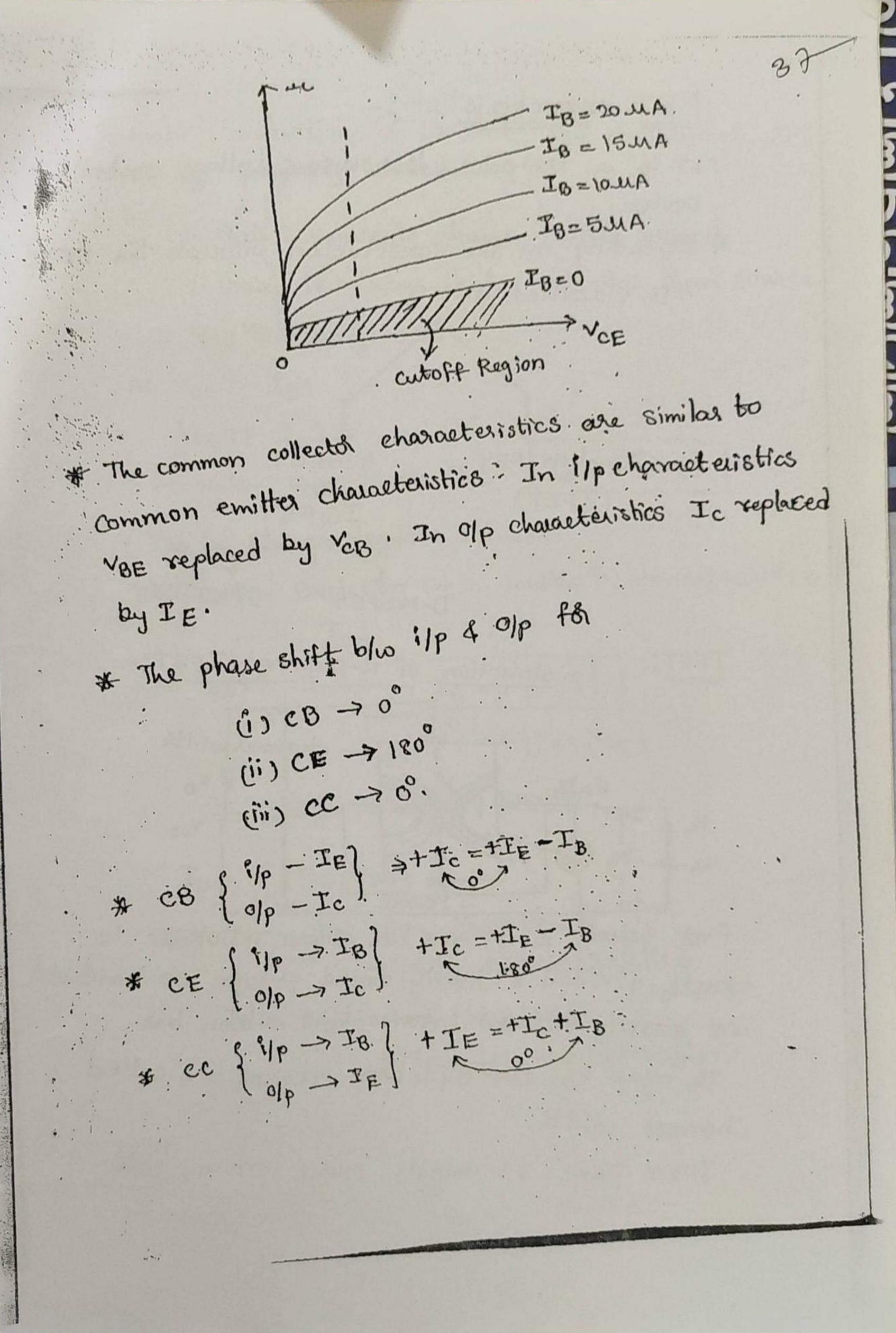

Output characteristics:-

Je vs vois when  $T_E = const \int_{cit}^{(1)} T_E = 0$

Case (i) when IE=0

i.e B&E terminals o.C.

The char. of the transister in this case is similar the char. of a R.B.PN-Iwaction diode. \* AS VOBT Temp across Vote \* Bre akage of covalent. bonds of in c'4 Base. \* Inot Ipot = Tot Ich Cut off Region AS VOBA ICA When IE 70. · Let IE = ImA (Constant). - Depletion region width 1, Base width 1 - Recombination Rate in Base V AS VCBTT ICTT Ict to the max value of IE only. once Ic=IE VCB1 Ic = constant = 1mA:

Scanned by TapScanner

case cils when e'a E -> 3.c

\* All the maj. corriers of E' collecter

by B'. There is no change in current

due to E: blu B'4 E in case (i) f

case (ii)

\*The no. of hotes collected by the E' from the Base of ... The hole current blu B'4 E = 1

\* To maintain IB as const. increases the VBE value.

i.e to get a particular value of IB the req. value of

VBE is More in this case compared to case (i).

Case (iii) when VoE to Let VoE=1v.

\*The noise e's collected by B' from E'V

The e current blu B'4 E'V

The noise holes collected by E' from BT.

The hole current blu B'FE'T

The resultant current B'FE V, IBV

To maintain IB as constant TVBE i.e to get a

particular value of JB the required value of VBE is more in this case compared to case (ii). output characteristics:-Ic Vs VCE when IB = const Case (1): - when IB=0 + B + E terminals are O.C Ic = Inc+ Ipo AS VCET ICT case (ii): - when IB +0 Let IB = 5MA. JE must be F.B VCE = 0 VB = VX+VE. (i) when VCE < VBE => JC-7F-B -> saturation Region. (ii) when YCE > VBE => JC -> R.B -> Active Region.

# FET characteristics:-

FET is a unipolar, low noise & voltage controlled.

Device.

\* pepending on the construction principle the FETS are classified into

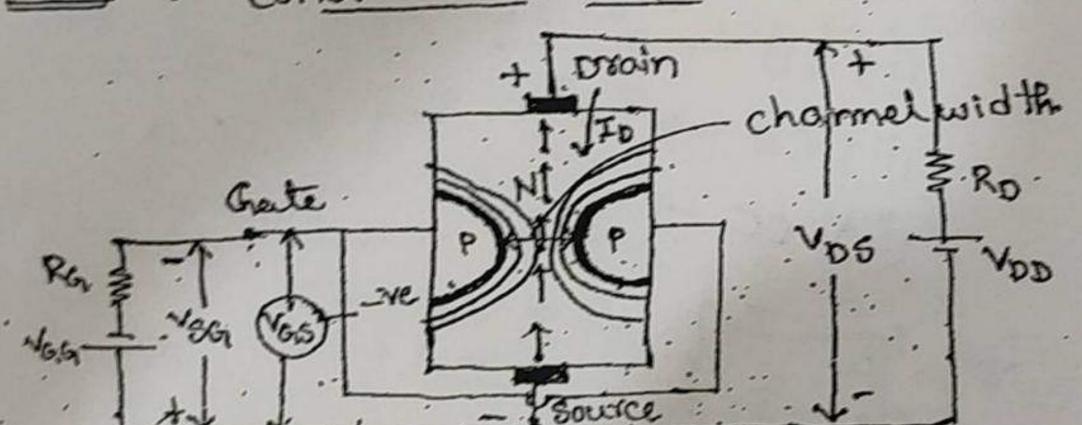

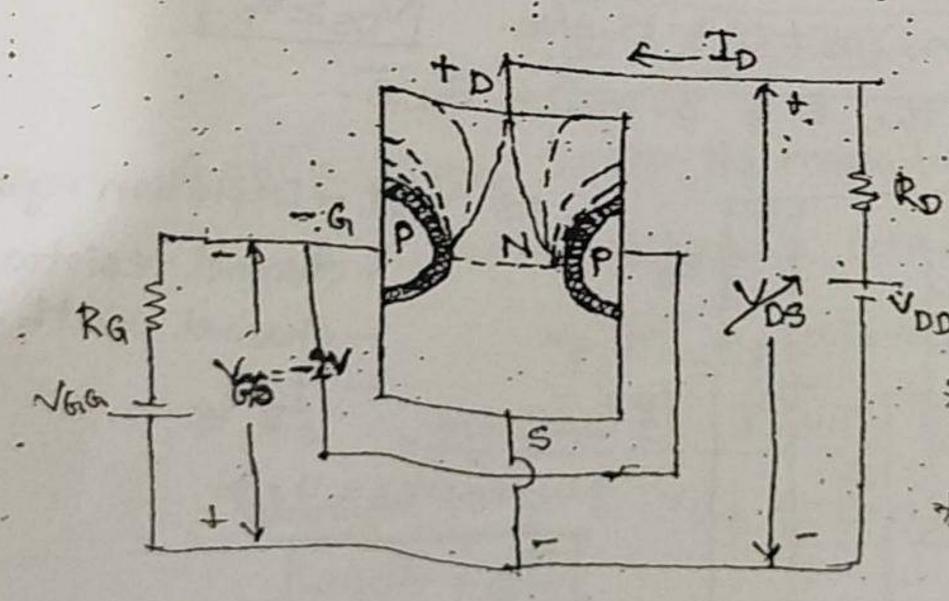

JFET:- construction of N-chamnel JFET:-

first select. The N type box whose resistance is exactly divided 2 heavily doped p-type semiconductor one exactly diffused into N-type silicon box.

The gap blus two depletion regions are called channel width.

JFET have 3 terminals source; Drain, gate.

To make conduction of current the N-chammel JFET must be properly biased.

1. Gate - source is always Reverse biased. 2- Drain is always higher potential than source. Vos is always +ve.

AS VOST IDT

VOSTT IDT T

\* ID value depends on Mos. I In = f [ Mos]

> Vos 95 always negative values.

AS Vast - Depletion region widths 7, channel width 1

AS VGSTT IDIL ID = f [VGS]

ID = F [YGS, YDS]

-> Voltage controlled Device.

ID = f [Vas, Vos]

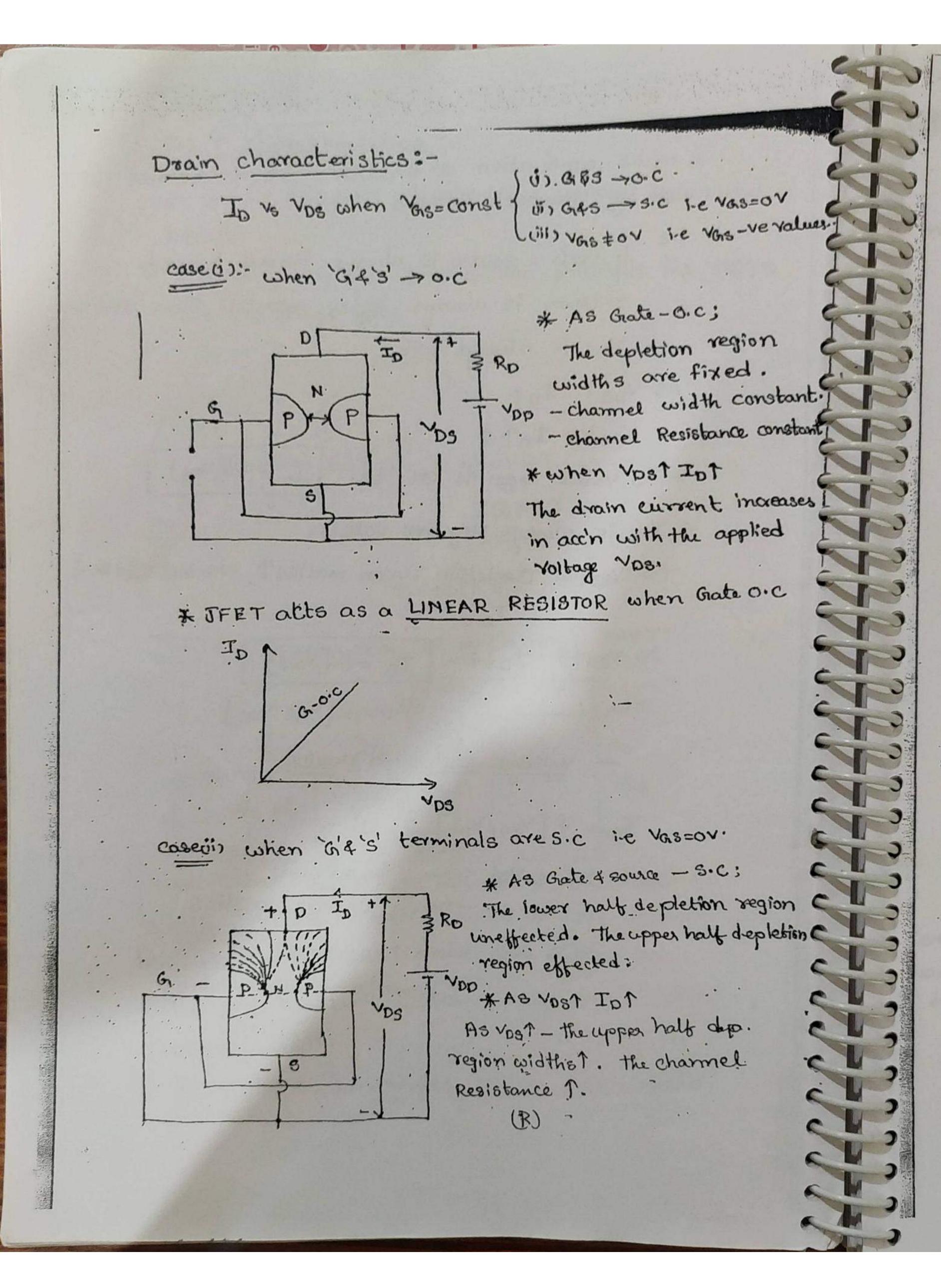

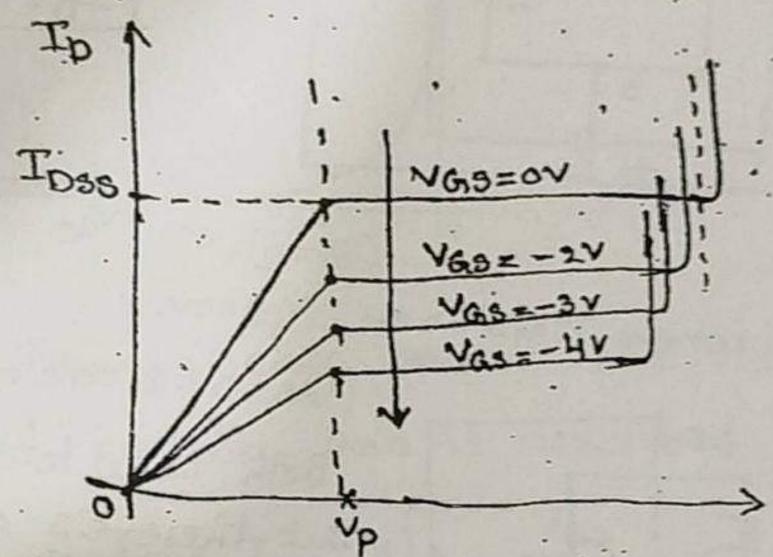

In vs Vos when Vas = const

- Drain characteristics

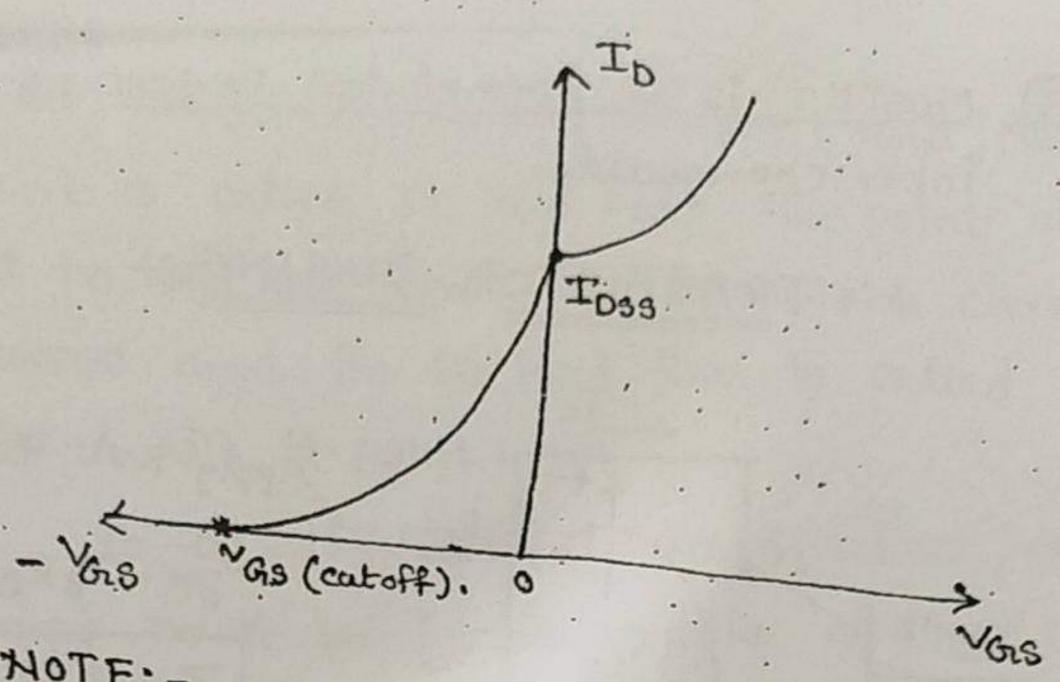

ID vs Vas when Vpg=const

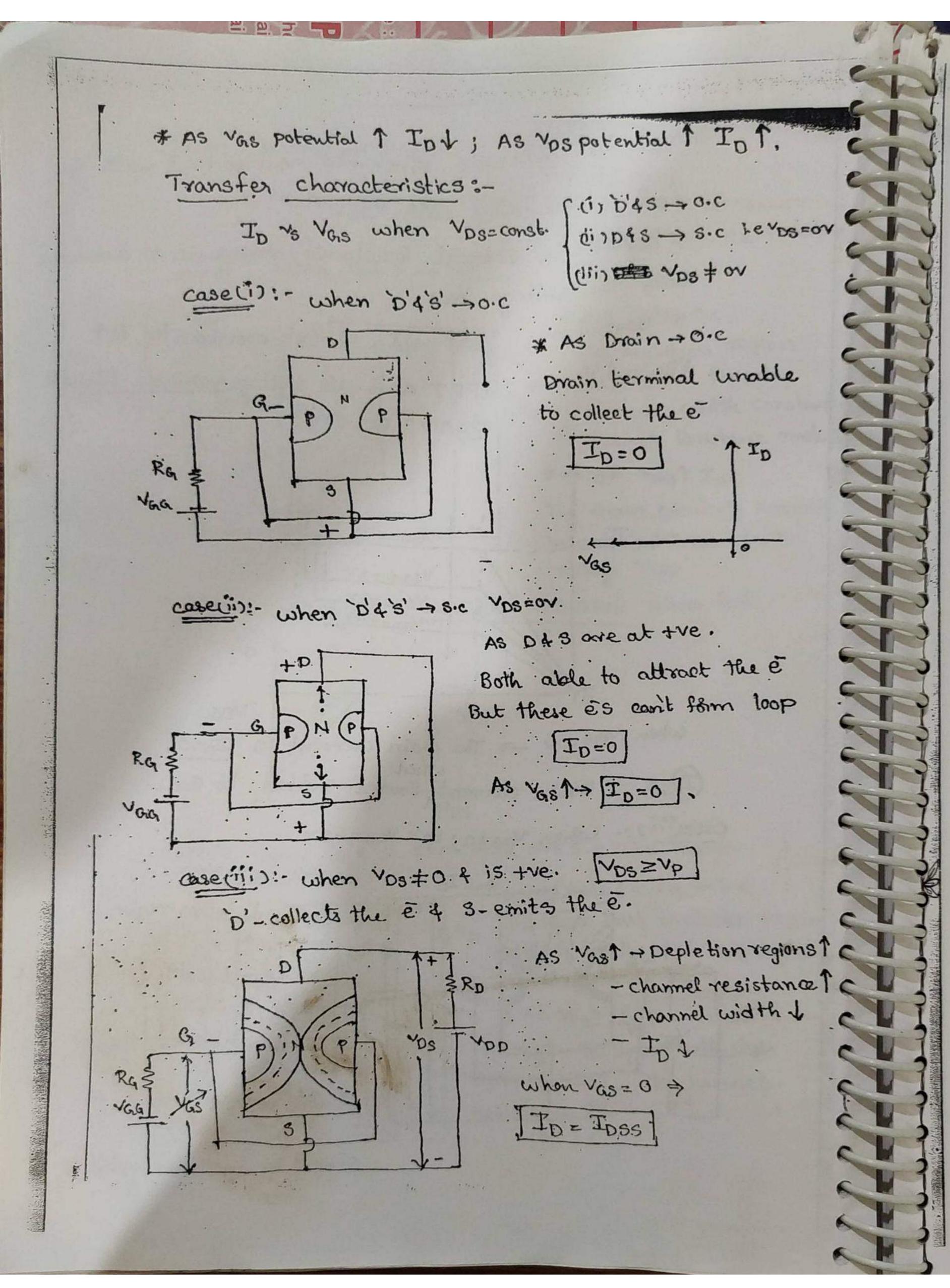

- Fransfer characteristics

# Vost IDT RT upto pinch-off voltage (Vp) upto Vp, IDT in accordance with VDs.

\* Beyond vp, channel Resistance varies in accordance with the voltage vps.

\* Beyond Vp; VDST -> ID almost constant. RT

\*Beyond Vp, -> JFET acts as voltage variable Resister

(3) VVR (3) V2R.

when vois=or -> The depain current is IDSS.

Thiss -> Drain current source shorted to Gate.

Caseciii):- When Vas+0; Let Vas=-2v

foi Vas = -2V

The depletion region & Ro: widths?

. -> channel width 1.

TOI & cool

\* The current is less than case (i).

\* As vost-upto Vp Jot

RT (very small)

beyond up Ip-ralmost constant Ri

Scanned by TapScanner

At some particular voltage depletion region occupies the channel width  $\Rightarrow$  channel width becomes  $\Rightarrow |Tp=0| \Rightarrow The JFET becomes cutoff! The potential is called <math>V_{0.8}$  (cuttoff) voltage.

VGS (Catoff)

\* The Transfer char. son of the JFET in the shape invested parabola. and is described by the equation.

$$: \mathbf{I}_{D} = \mathbf{I}_{DSS} \times \left[ 1 - \frac{\mathbf{V}_{GS}}{\mathbf{V}_{GS}(\text{cutoff})} \right]^{2}$$

\* when Vas=0 => To= IDSS.

\* for a given JFRT the magnitudes of pinch-off voltage.

and cut-off voltages are same.

# for a M-channel JFET: the pinch-off voltage (Vp) is always + ve & vas (cutoff) is always - ve.

Ph-An n-charmel JFET has IDSS = 12mA the Vp = 5V calculate the require value of Vois voltage to get

$T_{D} = 8mA$   $T_{D} = T_{DSS} \left[ -\frac{V_{as}}{V_{as}(autoft)} \right]^{2}$   $8mA = \frac{4}{12mA} \left[ -\frac{V_{as}}{-5V} \right]^{2}$  12mA 12mA 12mA  $14 = \left( 1 + \frac{V_{as}}{5} \right)^{2}$   $1 + \frac{V_{as}}{5} = \pm \frac{1}{2}$   $\frac{V_{as}}{5} = \pm \frac{1}{2}$   $\frac{V_{as}}{5} = -0.5V, -1.5V$   $\frac{V_{as}}{5} = \pm \frac{1}{2}$   $\frac{V_{as}}{5} = -2.5V$

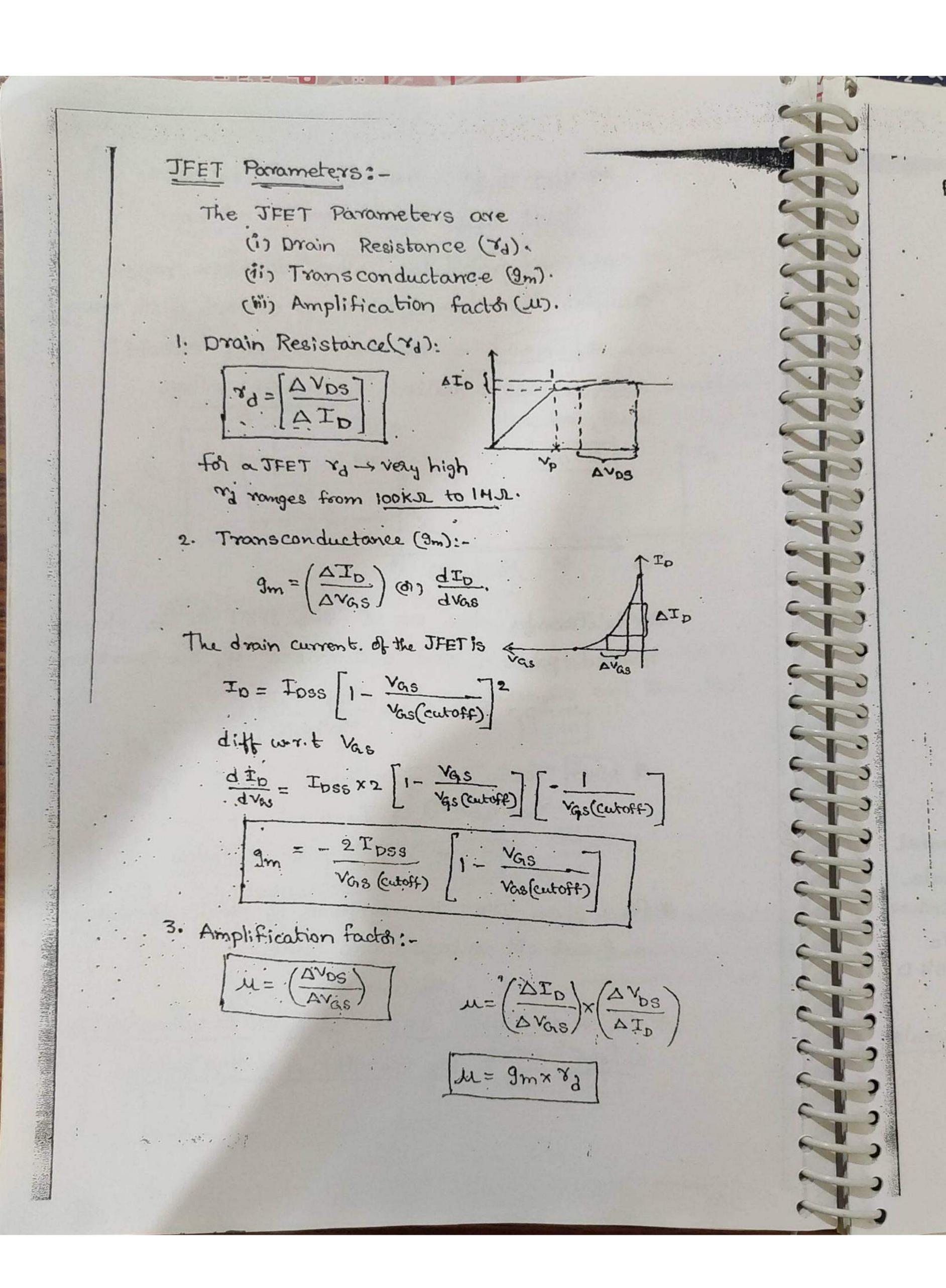

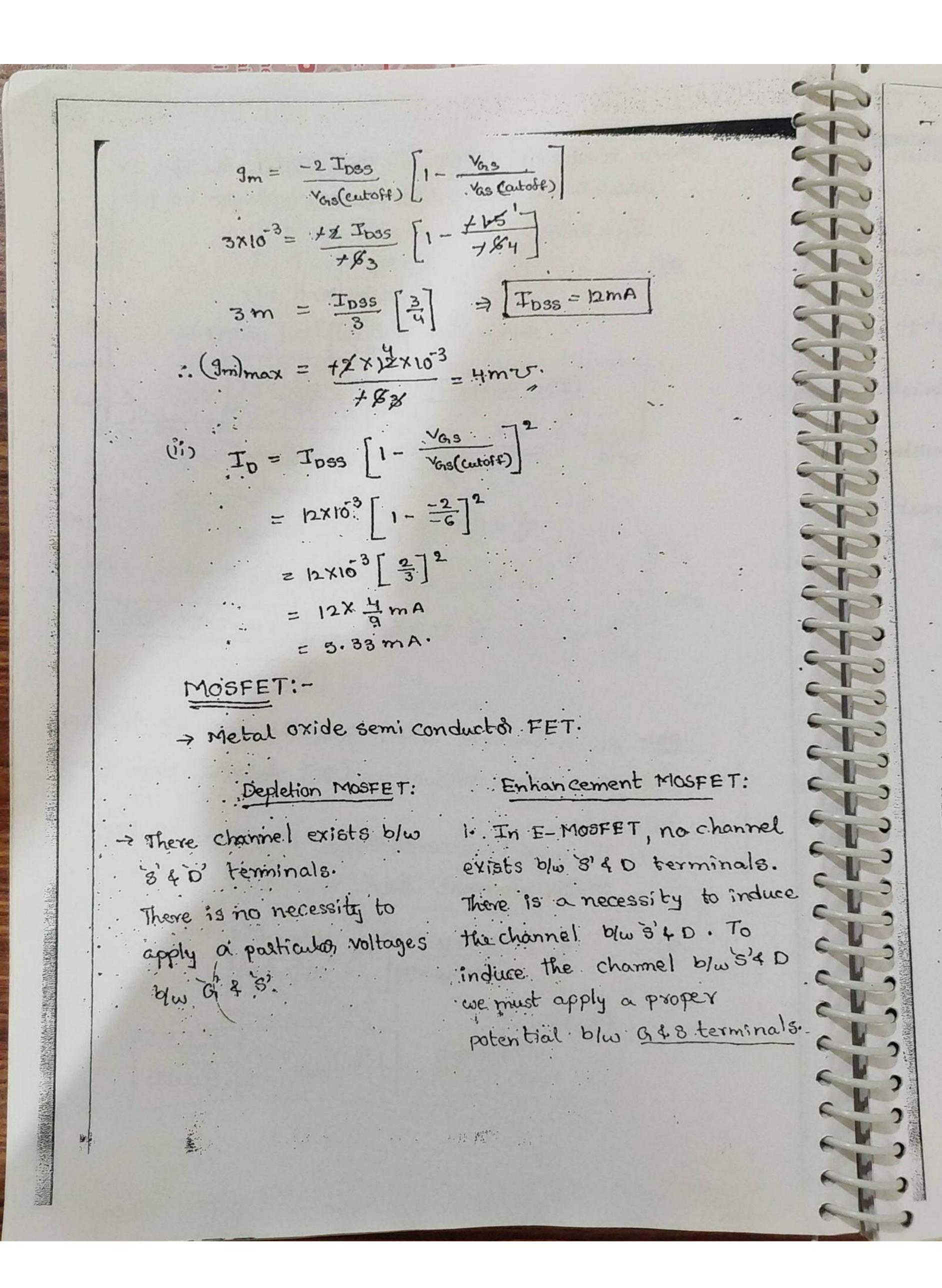

Pb:- An n-channel JFET has the Vp=-6V the JFE? offers a trans conductance (9m) of 3m Tr when Vas=-1.5

alculate

1. The max transconductance offered by the TFET.

501,

$$g_m = \frac{-2 \text{ T}_{D53}}{\text{V}_{G5} \cdot (\text{cutoff})} \left[ \frac{\text{Vas}}{\text{Vas} (\text{cutoff})} \right]$$

(9m) max  $\left| \text{VGr}_{5} = 0 \right| \left( \frac{9m}{\text{max}} \right) = \frac{-2 \text{ T}_{D33}}{\text{VGs} \cdot (\text{cutoff})}$

#### Depletion MOSFET

- we can apply any potentials blw G' 4's'.

VGis { tve voltages }

-ve voltages }

N - channel D-MOSFET.

P-channel D-MOSFET

### Enhancement MOSFET.

- For N-channel E-MOSFET

\*\*Vors is always tre & VG3 > VG3

(threshold)

- when YGB = YGS(th):-

This is the min voltage to induce the channel. The channel is formed by a min no of chang positicles once channel formed by the charged positicles, these charged positicles are remains fixed for entire operation.

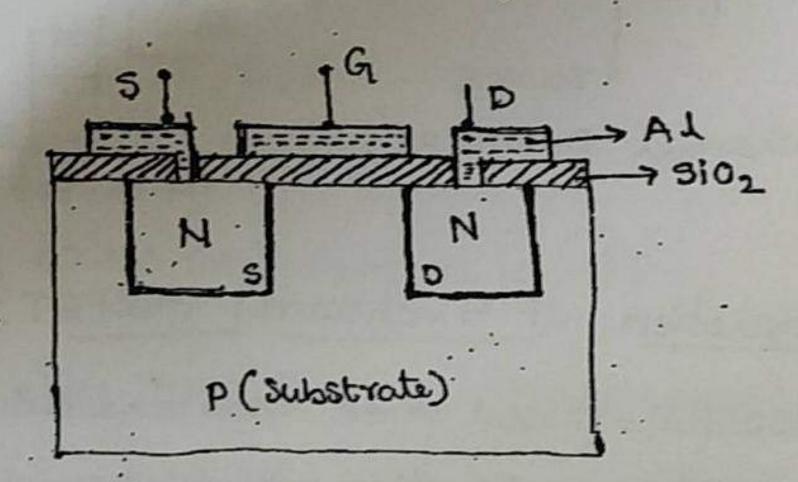

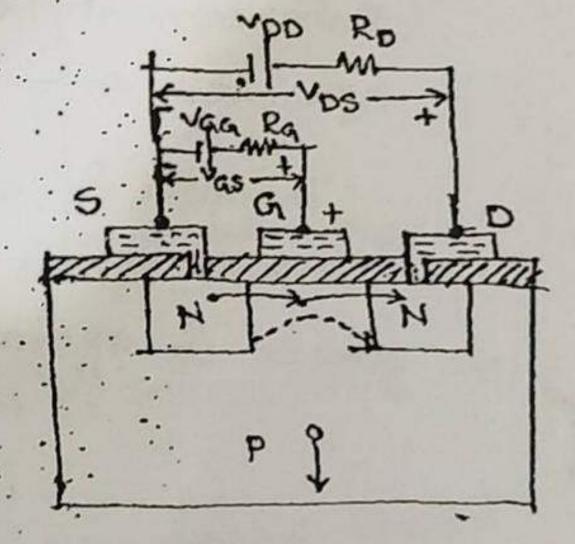

## Construction of N-channel MosfeT:-

MOSFET - (metal oxide semi conductor FET)

In the construction of N-Channel Mosfet, we are selecting the p-type substrate. The substrate is used to protect the device from the applied electric fields.

> Two heavily dopped N-type sections are diffused into the substrate by maintaing the proper gap.

The gap blue two N-sections is called "Channel length" (81) space. = 1x103x2-54x102m

Channel length = 1 mil - length - = 25.4 um ~ 26 um;

- The depletion regions formed under open ckt condition only.

- -> one acts as source and onether is acts as brain.

- -> over the surface of substrate an oxide layer is grown except where source 4 dearn maintain to be contact.

- is very high (1010 to 1052).

- -> This layer protects. the device from further fabrication steps.

- 7 The 1/p resistance of Mosfet is equal to the resistance of 5:00

- over this surface a metal layer is grown that must cover the entire space blu the two end sections.

This metal is - Aluminum

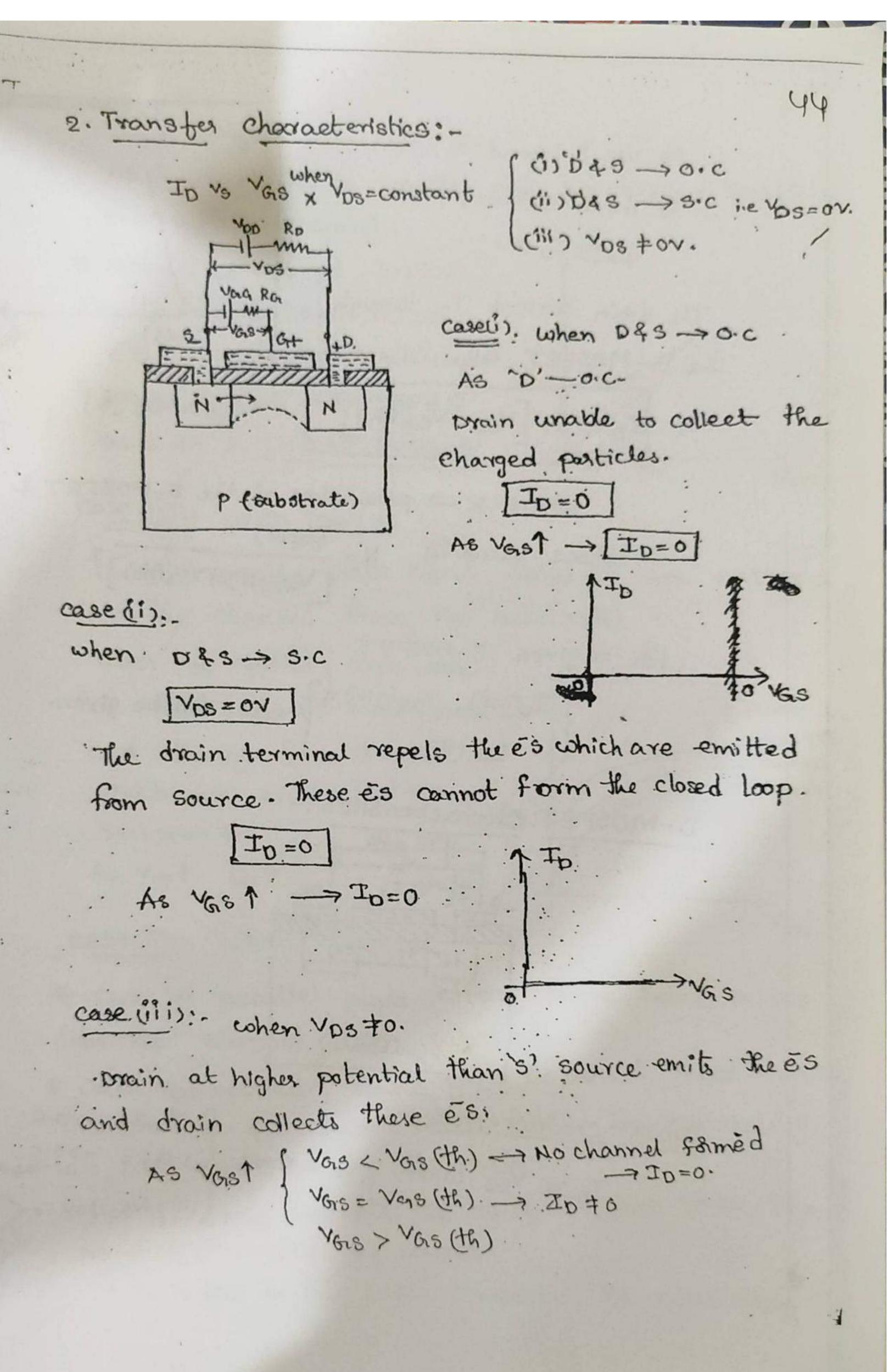

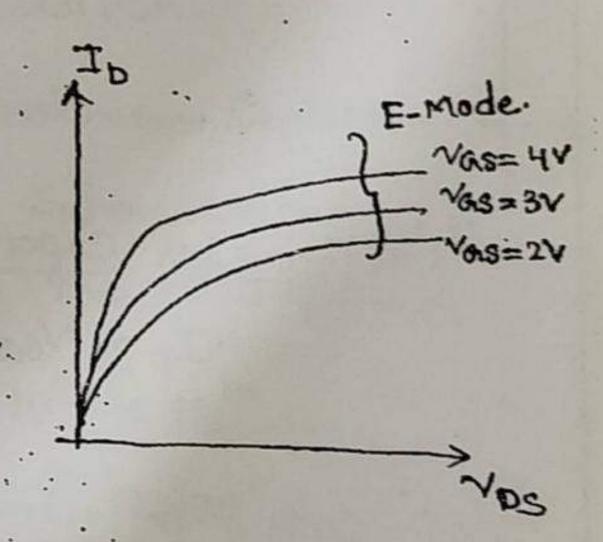

E= MOSFET characteristics:

ID = f ['Vasi'Vos]

\* Ip. vs. vos when vas = const.

-> prain characteristics.

# IDNS. VGS when Yos = const.

Transfer characteristics.

#### 1. Drain characteristics:

ID vs Vos when Vas=constant (is G'4's' -> o.c (is) G'4's' -> s.c (iis) Vas = ov

Case (i) when 'G'43 -> o.c

As Gate O.C -> No charmel famed ywo D'&'s' terminals.

[Jo=0]

· As Vost = ID=0

Caseciis. - when G&S -> s.c. le Vaszov.

As VGS=OV, No channel formed. blus s& D'

ID=0], AS Vost ⇒ ID=0

Case(iii): - when Vors \$ 0. \ Vors \ Vors (threshold)

Vors = Yors (threshold)

Vors > Vors (threshold)

(a) for Vors < Vas(th)

- No charmel is formed [To=0]

As Vost Toco

(b) As VG18= VG18(Ph)

At this potential channel is

\* Due to parallel plate effect,

the minority carriers (Es) of

Substrate comes blu s' & D'

and forms a layer called INVERSION LAYER.

\* These es are remains fixed for entire operation.

AS VDST TOT TO TED

Vois = 6V.

Vois =

(c) As Vas Vas(th) Let Vas=4.V

bue to posallel plate effect some more é enters into the charmel. 4 ave considered as free és.

when vos applied - Drain able to collect these es

Now In is more in this case compared to case(b)

As vost Int.

The mode of operation in which the drain current increases as the Vas voltage increases is called Enhancement mode of operation. The E-MOSFET operated only in Enhancement mode only.

The mode of operation in which the Drain current decreases as Vas voltage increases is called Depletion mode of operation. Ex:- JFET.

45

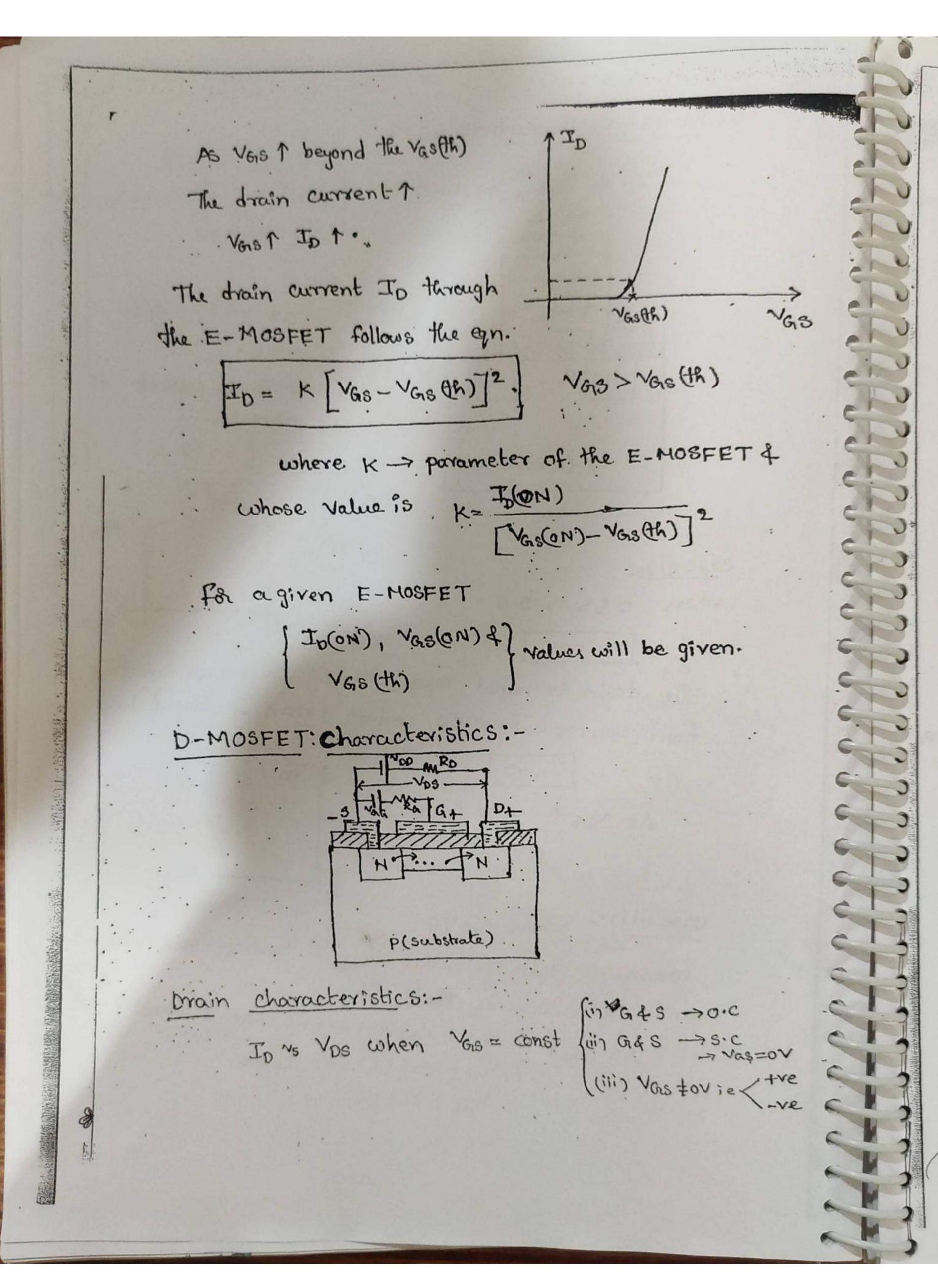

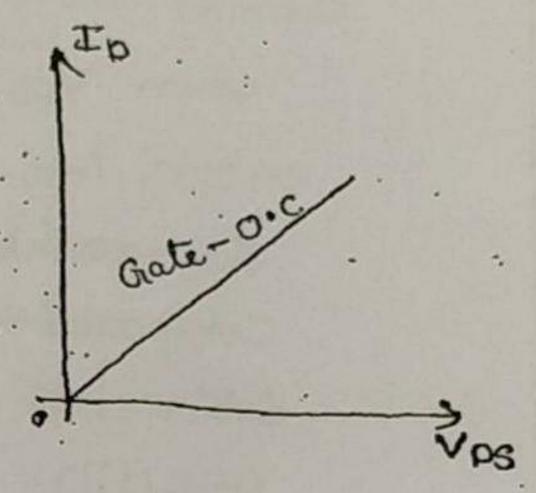

case ci): when dif s .- > o.c

As G-O-C -> Due to parallel plate no charge d particles enters into channel.

\* when YDS applied, source emits the es and these es are collected by Drain \* when G-> O.C. -> D-MOSFET acts as a LINEAR Resista.

# Case (ii): - when Yors +ve

Due to paratlel plate effect some és are entered into the channel from the substrate.

when vos applied, drain able to collect the es from scince and the es from channel which are entered from substrate.

As Most IDT

### case (iii):- when Vastov

\* Due to parallel plate effect some holes enters into the channel from substrate.

\* when vos applied, source emits the Es & these e enter into channel & recombine with holes. The remaining es are collected by the drain.

.. The drain collects the no. of és less than the no. of és emitted by source.

M. This less in this case. compared to case (ii)

#### case (iv): - When Vas -ve

Due to parallel plate effect the no. of holes enters into channel more in this case compared to case (iii).

when Vos applied, the e emitted from source enters into channel and recombine with holes. The recombination rate in this case is more Compared to case (iii). The nord es collected by drain less ID is less in this case compared to case (iii).

Vos=47 E-Mode of operation.

Vos=27 Vos=27 D-mode of operation.

Vos=-27 D-mode of operation.

Transfer characteristics:-

In vo Vas when Vos= const (ii) D'45 -> s.c. le. Nos=ov

case (iii): when YDS =0.

Drain is higher potential than s. source emits

the es & drain collects these es.

→ when Vas=ov ID= IDSS

AS Vast (+ve direction) = IDT.

· Vois 1 (-ve direction) => IDV.

NOTE:-

13 when Grate - o.c:

JFET acts as a LINEAR RESISTOR.

11

D-MOSFET

E-MOSFET

" open switch.

- 2) JFET operated only in Enhancen Depletion mode E-Mosfet operated only in Enhancement 11 D-Mosfet operated in both the modes.

- (3) JFET input Resistance is 108 to 10%, MOSFET input Resistance is 10.00 to 10.15 s.

- (4) Gate current of the JFET in the order of hano amp". . Gate current of the Mosfet in the older of · Pico amp"

- (5) The Size of MOSFET Smaller than that of JFET.

- (6) The MOSFET3 are used in VLS1 4 ULS1 CKts who as. JFETS are restricted to Digital Logic ckts.

Mosfet is a symmetrical Device i.e sfb' Inter changeable. TRANSISTOR BIASING:-Apply KVL to ilp loop & Rc VBB-IBRB-VBE=0 Apply KVL to olp loop Vcc-IcRc-VcE=0 \* on x-axis- y-axis component is o' . (Ic=0) VCE = VCC - ICRC VCE = Vcc / -> Max of p voltage \* on Y-axis - x-axis component is o' > max o/p Current. pc load line 25 u.A. JB = 20MA JB=13.UA a (vcta, tca) IB=KUA TB= SUA Ica cutoff  $T_B = 0$ Rogion + x(vcc,0)

Scanned by TapScanner

The line joining the cut off point and the saturation point is called DC load line. The point of intersection of DC load line and the transists characteristic curve and the DC load line is called operating point (31) Q. point.

point must be in the middle of the Dc load line.

(8) near about the middle of the Dc load line.

Q (VCE, Ic).

Ic = BIB + (HB) Io.

Due to collection of charged particles by c'

temp across the 5n Jc?

As Temp? => Io, B&. VBE varies.

Effect of temp on Io, B4 VBE:-

(ii) ASTA BA.

For 50°CA temp. B value of Gre transister Dombles.

For 100°CA 11. 11 of si 11. "

(iii) ASTT VBE 1.

F8. 1°CT temp. VBE 1 by 2.5mV

"Ic effected more by To".

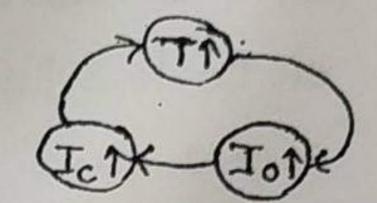

$AS T1 \Rightarrow Io10$   $AS T1 \Rightarrow Io10$  AS Io1 = Ic1  $AS Ic1 \Rightarrow T1$

Due to the collection of charged particles by the collector temp across the Junction Je increases. It becomes the process. At some particular stages the temp across the Junction becomes max and the breakdown of the collector Junction takes place, this process is called thermal Runaway. This is due to unstability in the transistor simply the self distruction of an unstabilized transistor is called thermal Runaway.

stabilization:-

Io, VBE, & B due to temp.

the transister must be stabilised.

The process of making the operating point independent of the variations in Io, VBE, B due to temp in termed as stabilization.

The process of keeping the operating point in the active region is termed as stabilization. The stability of a transists is measured in stability facts.

Else the transister operated in saturation Ragion. If the transister operated in saturation Region - VCE = VCE (80t) = 0.2 V -> Si.

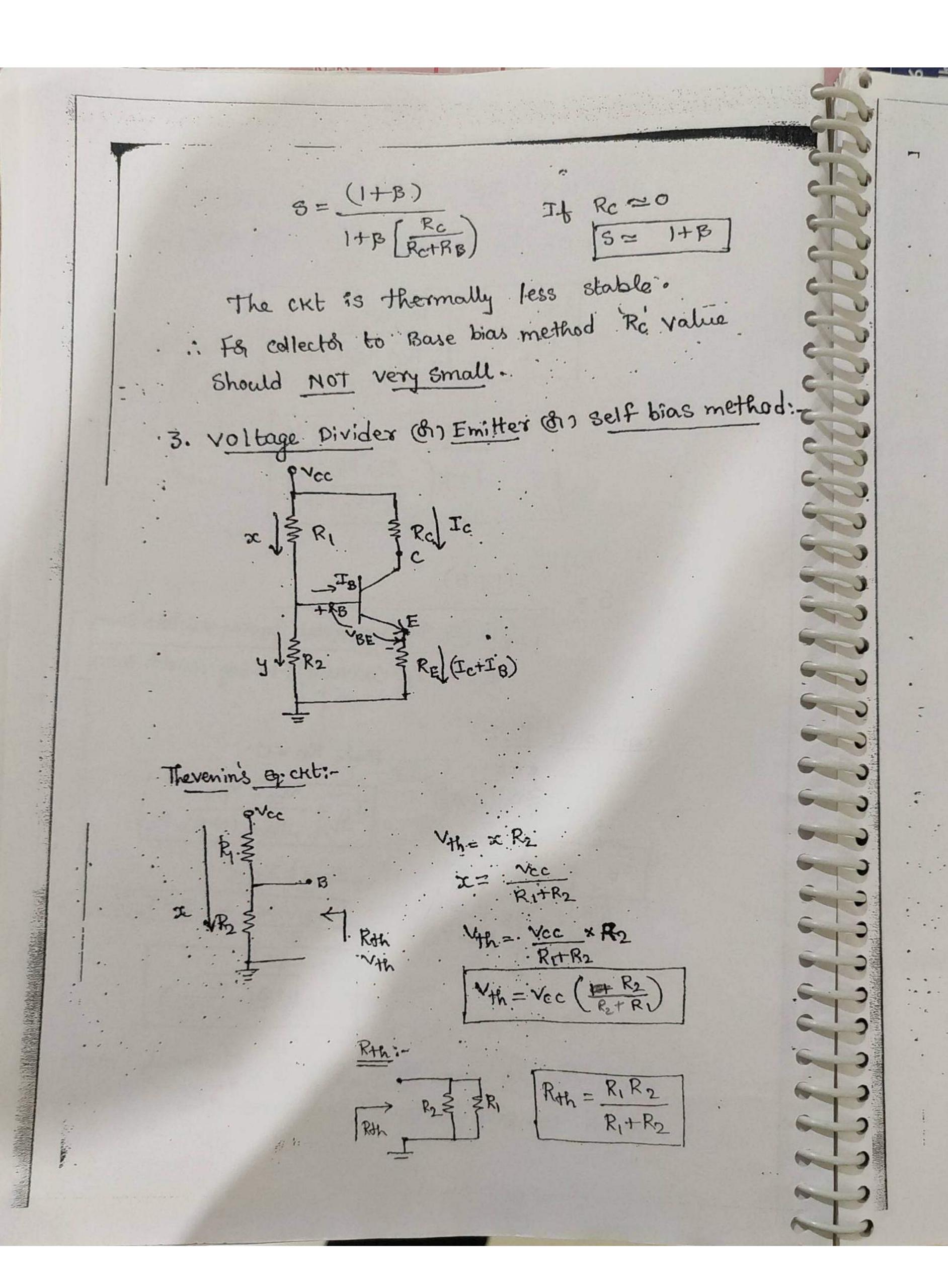

O.1 V -> Ge. Stability facts: To calculate 5 take i/ploop eq. VCC - IBRB -VBE = 0 Diff wiret Ic O - dIB x RB-O = O S= (1+B) \* The fixed bias CKt is thermally less stable. \* To increase the thermal stability of this ckt connects à Resiston at emitter. Apply KVL to ilp loop VCC-IBRB-VBE-(IC+IB)RE-OC Ic = BIB Assuming the toansistor RE(IB+Ic) the Active region. (Ic+IB) = (1+B) IB VCC-IBRB-VBE-(1+B)IBRE=0 Ro + (HB) RE

Apply KVL to olp loop,

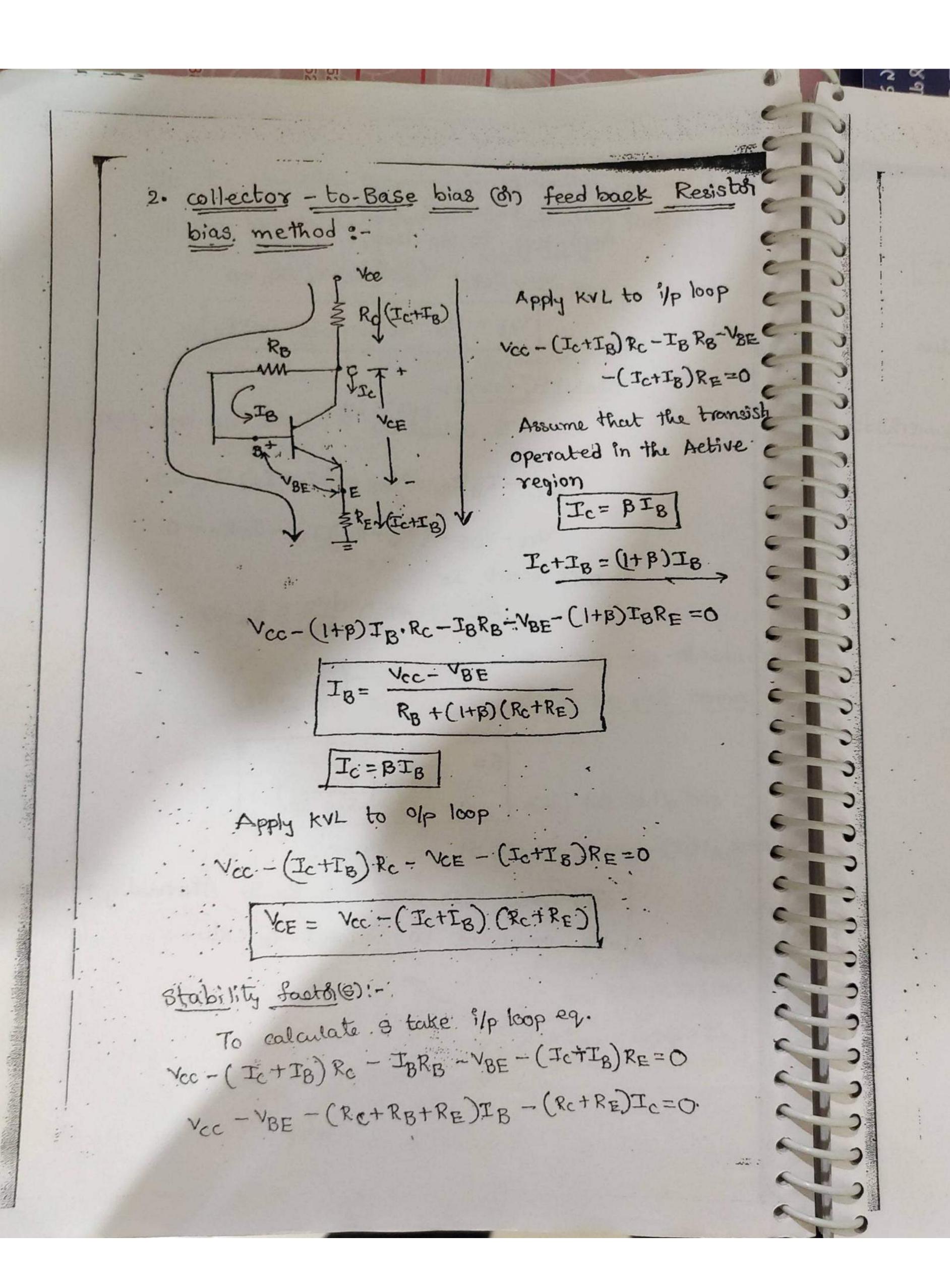

Stability factor:-

To calculate 3, teike i/p loop egn,

Diff wirt Ic

$$\frac{dT_B}{dT_C} = -\left(\frac{R_E}{R_B + R_E}\right)$$

· AS Pr >1., 32(HB).

The fixed bias ext with RE is thermally more stable compared to without RE ckt.

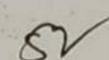

Apply KVL to 1/p toop:

Vth - IBRER-VBE - (IctIB) RE:

Assume that the transistor

Operated in the Active

Region.

Ic = BIB & (Ic+IB)=(HB

$$T_{B} = \frac{V + h - V_{BE}}{R + h + (1 + \beta)R_{E}} + T_{C} = \beta T_{B}$$

Apply KVL to % loop:

Stability factor: -

$$5 = \frac{1+\beta}{1+\beta\left(\frac{R_E}{R_{Hh}+R_E}\right)}$$

$$1 = \frac{1+\beta}{1+\beta\left(\frac{R_H}{R_E}+1\right)}$$

if RHR ~ 00 > Smy (1+B).

The ckt is thermally less stable.

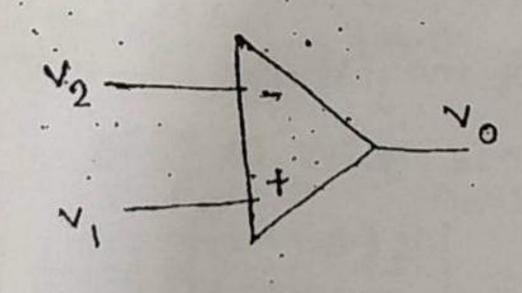

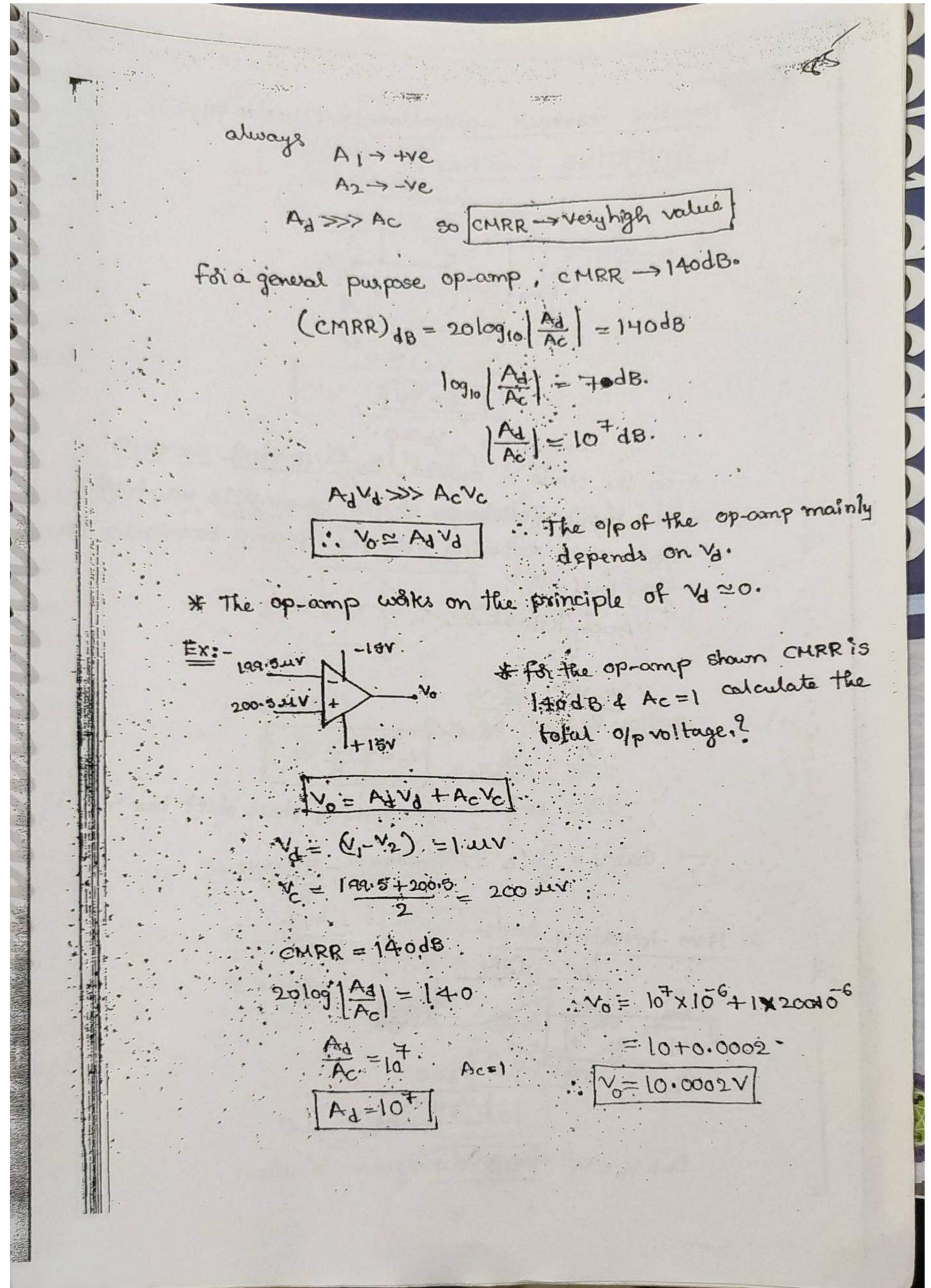

Operational Amplifiers:op. Amp characteristics: Ideal char: -> R1=00. 1. input resistance -> very high -> Ro =0 .. 2. output resistance -> very low -> : AOL = 00. 3. openloop gain (AoL) -> voug high -> very high -> Bw = 00. 4. Bound width -> 'offset voltages =0 -> very low 5. Offset voltages > very high -> CMRR = 00 e. Common Mode Rejection Ratio -> very high -> 3R = 00 7. Skew. Rate \* A Basic op-omp consists minimum terminals. AOL Olp 2 1/p terminals 3. 2 supply voltages. (v+,v-) \* Remaining terminals depends on its application. Vo = AOL (V1-V2) va - Differential Tip voltage No= A01 Vd where No = Investing terminal voltage. | Gain -ve VO = AOL (0- V2) Vo = - AOLV2 180° of phase shift blw

when V2=0:

\* the sign represents 0° of phase blue vo & vi.

Vi-> non investing terminal voltage

Vo = AOL (VI-O)

Va Tilvi

$V_0 = A_{0L}(V_1 - V_2)$   $V_0 = A_{0L}(V_0)$   $* A_{0L} = V_0$   $V_0$

The an op-amp Aol is very high, to get this

'Y=0 (very low).

Vo = AOL Va) -> Pinite value

→ for an ideal op-amp Aoi=00 — To get this value Yd=0:

No = 407 19 = 0.

> But practically the olp of the op-amp is not equal to 24

So that the set output of the op-amp not only depen

on the differential set ilp voltage But also depends

on common made (Avg signal).

V<sub>1</sub> = Mon inverting terminal

Voltage.

V<sub>2</sub> = Provesting terminal voltage

A<sub>1</sub> = Grain due to V<sub>1</sub> alone

A<sub>2</sub> = Grain due to V<sub>2</sub> alone

V<sub>4</sub> = (V<sub>1</sub>-V<sub>2</sub>) → Differential 1/p voltage.

E C

Total of voltage

$$(y_0) = \begin{cases} v_0 + v_2 \\ v_0 = \begin{cases} v_1 + v_2 \\ v_1 = v_2 \end{cases} \end{cases}$$

We know that

$v_1 = v_1 + v_2 \\ v_2 = v_3 + v_2 \end{cases}$

$v_1 = v_3 + v_2 \\ v_2 = v_1 + v_2 \end{cases}$

$v_1 = v_3 + v_4 + v_2 \end{cases}$

$v_2 = v_1 + v_2 \end{cases}$

$v_3 = v_4 + v_4 + v_2 \end{cases}$

$v_4 = v_1 + v_2 \end{cases}$

$v_1 = v_3 + v_4 + v_2 \end{cases}$

$v_2 = v_1 + v_2 \end{cases}$

$v_3 = v_4 + v_4 + v_2 \end{cases}$

$v_4 = v_2 + v_3 + v_4 \end{cases}$

$v_2 = v_3 + v_4 \end{cases}$

$v_3 = v_4 + v_4 + v_4 \end{cases}$

$v_4 = v_4 + v_4 + v_4 \end{cases}$

$v_2 = v_3 + v_4 \end{cases}$

$v_3 = v_4 + v_4 \end{cases}$

$v_4 = v_4 + v_4 \end{cases}$

$v_4 = v_4 + v_4 \end{cases}$

$v_5 = v_5 + v_5 \end{cases}$

$v_6 = v_6 + v_6 \end{cases}$

$v_7 = v_7 + v_7 \end{cases}$

$v_8 = v_8 + v_8 \end{cases}$

$v_8 = v_8 + v_8 \end{cases}$

$v_9 = v_9 + v_9 \end{cases}$

$v_9 = v_9 + v_9$

$v_9 = v_9 + v_9 + v_9 + v_9$

$v_9 = v_9 + v_9 + v_9 + v_9 + v_9$

$v_9 = v_9 + v$

Scanned by TapScanner

$$V_0 = \frac{R_2}{R_1} \left( || I_R| + V_1 - V_2 + I_R|^2 \right)$$

$$= \frac{R_2}{R_1} \left( || (V_1 - V_2) + (V_1 - V_2)|^2 \right)$$

$$V_0 = \frac{R_2}{R_1} \left( || (V_1 - V_2) + (V_1 - V_2)|^2 \right)$$

$$V_0 = \frac{R_2}{R_1} \left( || (V_1 - V_2) + (V_1 - V_2)|^2 \right)$$

$$V_1 = \frac{R_2}{R_1} \left( || (V_1 - V_2) + (V_1 - V_2)|^2 \right)$$

$$V_2 = \frac{R_2}{R_1} \left( || (V_1 - V_2) + (V_1 - V_2)|^2 \right)$$

$$V_3 = \frac{R_3}{R_1} \left( || (V_1 - V_2) + (V_1 - V_2)|^2 \right)$$

$$V_4 = \frac{C}{R_1} \left( || (V_1 - V_2) + (V_1 - V_2)|^2 \right)$$

$$V_1 = \frac{C}{R_1} \left( || (V_1 - V_2) + (V_1 - V_2)|^2 \right)$$

$$V_2 = \frac{C}{R_1} \left( || (V_1 - V_2) + (V_1 - V_2)|^2 \right)$$

$$V_4 = \frac{C}{R_1} \left( || (V_1 - V_2) + (V_1 - V_2)|^2 \right)$$

$$V_6 = \frac{C}{R_1} \left( || (V_1 - V_2) + (V_1 - V_2)|^2 \right)$$

$$V_7 = \frac{C}{R_1} \left( || (V_1 - V_2) + (V_1 - V_2)|^2 \right)$$

$$V_8 = \frac{C}{R_1} \left( || (V_1 - V_2) + (V_1 - V_2)|^2 \right)$$

$$V_9 = \frac{C}{R_1} \left( || (V_1 - V_2) + (V_1 - V_2)|^2 \right)$$

$$V_9 = \frac{C}{R_1} \left( || (V_1 - V_2) + (V_1 - V_2)|^2 \right)$$

$$V_9 = \frac{C}{R_1} \left( || (V_1 - V_2) + (V_1 - V_2)|^2 \right)$$

$$V_9 = \frac{C}{R_1} \left( || (V_1 - V_2) + (V_1 - V_2)|^2 \right)$$

$$V_9 = \frac{C}{R_1} \left( || (V_1 - V_2) + (V_1 - V_2)|^2 \right)$$

$$V_9 = \frac{C}{R_1} \left( || (V_1 - V_2) + (V_1 - V_2)|^2 \right)$$

$$V_9 = \frac{C}{R_1} \left( || (V_1 - V_2) + (V_1 - V_2)|^2 \right)$$

$$V_9 = \frac{C}{R_1} \left( || (V_1 - V_2) + (V_1 - V_2)|^2 \right)$$

$$V_9 = \frac{C}{R_1} \left( || (V_1 - V_2) + (V_1 - V_2)|^2 \right)$$

$$V_9 = \frac{C}{R_1} \left( || (V_1 - V_2) + (V_1 - V_2)|^2 \right)$$

$$V_9 = \frac{C}{R_1} \left( || (V_1 - V_2) + (V_1 - V_2)|^2 \right)$$

$$V_9 = \frac{C}{R_1} \left( || (V_1 - V_2) + (V_1 - V_2)|^2 \right)$$

$$V_9 = \frac{C}{R_1} \left( || (V_1 - V_2) + (V_1 - V_2)|^2 \right)$$

$$V_9 = \frac{C}{R_1} \left( || (V_1 - V_2) + (V_1 - V_2)|^2 \right)$$

$$V_9 = \frac{C}{R_1} \left( || (V_1 - V_2) + (V_1 - V_2)|^2 \right)$$

$$V_9 = \frac{C}{R_1} \left( || (V_1 - V_2) + (V_1 - V_2)|^2 \right)$$

$$V_9 = \frac{C}{R_1} \left( || (V_1 - V_2) + (V_1 - V_2)|^2 \right)$$

$$V_9 = \frac{C}{R_1} \left( || (V_1 - V_2) + (V_1 - V_2)|^2 \right)$$

$$V_9 = \frac{C}{R_1} \left( || (V_1 - V_2) + (V_1 - V_2)|^2 \right)$$

$$V_9 = \frac{C}{R_1} \left( || (V_1 - V_2) + (V_1 - V_2)|^2 \right)$$

$$V_9 = \frac{C}{R_1} \left( || (V_1 - V_2) + (V_1 - V_2)|^2 \right)$$

$$V_9 = \frac{C}{R_1} \left( || (V_1 - V_2) + (V_1 - V_2)|^2 \right)$$

$$V_9 = \frac{C}{R_1} \left( ||$$

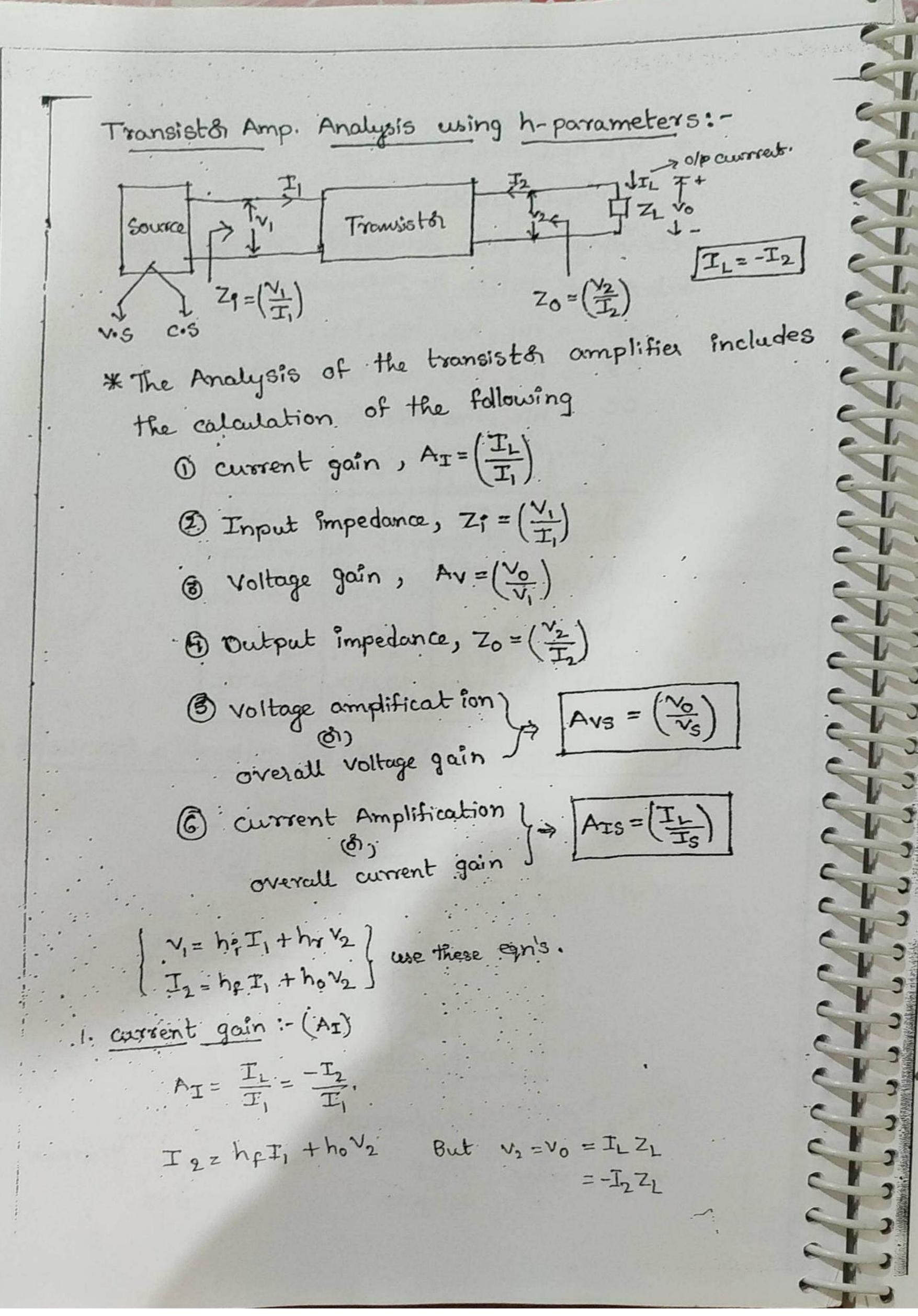

$$T_{2} = h_{f} \pm_{1} + h_{0} \left(-I_{2} Z_{L}\right)$$

$$\pm_{2} \left(1 + h_{0} Z_{L}\right) = h_{f} \pm_{1}$$

$$\left(\frac{I_{2}}{I_{1}}\right) = \frac{h_{f}}{(1 + h_{0} Z_{L})}$$

$$A_{I} = -\frac{I_{2}}{I_{1}} = -\frac{h_{f}}{(1 + h_{0} Z_{L})}$$

$$V_{1} = h_{1}^{*} I_{1} + h_{8} V_{2}$$

$$V_{1} = h_{1}^{*} I_{1} + h_{8} \left(-I_{2} I_{2}\right)$$

$$= I_{1} \left(h_{1}^{*} + h_{8} \left(-\frac{I_{2}}{I_{1}^{*}}\right) I_{2}\right)$$

$$Z_{1}^{*} = \frac{V_{1}}{I_{1}^{*}} = h_{1}^{*} + h_{8} A_{I} I_{2}$$

$$Z_{1}^{*} = \frac{V_{1}}{I_{1}^{*}} = h_{1}^{*} + h_{8} A_{I} I_{2}$$

3 Voltage gain:

$$Av = \frac{V_0}{V_1} = \frac{V_2}{V_1}$$

$$Av = \left(-\frac{I_2 Z_L}{V_1}\right)$$

$$\frac{V_1}{I_1} = Z_1 \Rightarrow V_1 = Z_1 I_1$$

$$Av = -\frac{I_2 Z_L}{Z_1 \cdot I_1} = \left(-\frac{I_2}{I_1}\right) \cdot \frac{Z_L}{Z_1}$$

$$A = \frac{A_1 Z_L}{Z_1}$$

(4) output impedance:

$$Z_{0} = \begin{pmatrix} V_{2} \\ I_{2} \end{pmatrix} | Load \rightarrow 0.c \ f$$

All the sources set equal to zero.

$$X_{0} = \begin{pmatrix} V_{2} \\ I_{1} \end{pmatrix} | Load \rightarrow 0.c \ f$$

All the sources set equal to zero.

$$X_{0} = \begin{pmatrix} V_{1} \\ I_{1} \end{pmatrix} | h_{1}$$

$$X_{0} = \begin{pmatrix} V_{1} \\ I_{1} \end{pmatrix} | h_{1} \end{pmatrix} | L_{1}$$

$$X_{1} = \begin{pmatrix} V_{1} \\ I_{2} \end{pmatrix} | L_{1} \end{pmatrix} | h_{1} \end{pmatrix} | L_{2}$$

$$X_{2} = \begin{pmatrix} V_{1} \\ I_{1} \end{pmatrix} | h_{0} \end{pmatrix} | L_{2}$$

$$X_{3} = \begin{pmatrix} V_{1} \\ I_{1} \end{pmatrix} | h_{0} \end{pmatrix} | L_{2}$$

$$X_{4} = \begin{pmatrix} V_{1} \\ I_{1} \end{pmatrix} | h_{0} \end{pmatrix} | L_{2}$$

$$X_{5} = \begin{pmatrix} V_{1} \\ I_{1} \end{pmatrix} | h_{0} \end{pmatrix} | L_{2}$$

$$X_{5} = \begin{pmatrix} V_{1} \\ I_{1} \end{pmatrix} | h_{0} \end{pmatrix} | L_{2}$$

$$X_{6} = \begin{pmatrix} V_{1} \\ I_{1} \end{pmatrix} | L_{2}$$

$$X_{7} = \begin{pmatrix} V_{1} \\ I_{1} \end{pmatrix} | L_{1} \end{pmatrix} | L_{2}$$

$$X_{7} = \begin{pmatrix} V_{1} \\ I_{1} \end{pmatrix} | L_{1} \end{pmatrix} | L_{2}$$

$$X_{7} = \begin{pmatrix} V_{1} \\ I_{1} \end{pmatrix} | L_{1} \end{pmatrix} | L_{2}$$

$$X_{7} = \begin{pmatrix} V_{1} \\ I_{1} \end{pmatrix} | L_{1} \end{pmatrix} | L_{1}$$

$$X_{7} = \begin{pmatrix} V_{1} \\ I_{1} \end{pmatrix} | L_{1} \end{pmatrix} | L_{1}$$

$$X_{7} = \begin{pmatrix} V_{1} \\ I_{1} \end{pmatrix} | L_{1} \end{pmatrix} | L_{1}$$

$$X_{7} = \begin{pmatrix} V_{1} \\ I_{1} \end{pmatrix} | L_{1} \end{pmatrix} | L_{1}$$

$$X_{7} = \begin{pmatrix} V_{1} \\ I_{1} \end{pmatrix} | L_{1} \end{pmatrix} | L_{1}$$

$$X_{7} = \begin{pmatrix} V_{1} \\ I_{1} \end{pmatrix} | L_{1} \end{pmatrix} | L_{1}$$

$$X_{7} = \begin{pmatrix} V_{1} \\ I_{1} \end{pmatrix} | L_{1} \end{pmatrix} | L_{1}$$

$$X_{7} = \begin{pmatrix} V_{1} \\ I_{1} \end{pmatrix} | L_{1} \end{pmatrix} | L_{1}$$

$$X_{7} = \begin{pmatrix} V_{1} \\ I_{1} \end{pmatrix} | L_{1}$$

$$X_{7} = \begin{pmatrix} V_{1} \\ I_{1} \end{pmatrix} | L_{1} \end{pmatrix} | L_{1}$$

$$X_{7} = \begin{pmatrix} V_{1} \\ I_{1} \end{pmatrix} | L_{1} \end{pmatrix} | L_{1}$$

$$X_{7} = \begin{pmatrix} V_{1} \\ I_{1} \end{pmatrix} | L_{1} \end{pmatrix} | L_{1}$$

$$X_{7} = \begin{pmatrix} V_{1} \\ I_{1} \end{pmatrix} | L_{1} \end{pmatrix} | L_{1}$$

$$X_{7} = \begin{pmatrix} V_{1} \\ I_{1} \end{pmatrix} | L_{1} \end{pmatrix} | L_{1}$$

$$X_{7} = \begin{pmatrix} V_{1} \\ I_{1} \end{pmatrix} | L_{1} \end{pmatrix} | L_{1}$$

$$X_{7} = \begin{pmatrix} V_{1} \\ I_{1} \end{pmatrix} | L_{1} \end{pmatrix} | L_{1}$$

$$X_{7} = \begin{pmatrix} V_{1} \\ I_{1} \end{pmatrix} | L_{1} \end{pmatrix} | L_{1}$$

$$X_{7} = \begin{pmatrix} V_{1} \\ I_{1} \end{pmatrix} | L_{1} \end{pmatrix} | L_{1}$$

$$X_{7} = \begin{pmatrix} V_{1} \\ I_{1} \end{pmatrix} | L_{1} \end{pmatrix} | L_{1}$$

$$X_{7} = \begin{pmatrix} V_{1} \\ I_{1} \end{pmatrix} | L_{1} \end{pmatrix} | L_{1}$$

$$X_{7} = \begin{pmatrix} V_{1} \\ I_{1} \end{pmatrix} | L_{1} \end{pmatrix} | L_{1}$$

$$X_{7} = \begin{pmatrix} V_{1} \\ I_{1} \end{pmatrix} | L_{1} \end{pmatrix} | L_{1}$$

$$X_{7} = \begin{pmatrix} V_{1} \\ I_{1} \end{pmatrix} | L_{1} \end{pmatrix} | L_{1}$$

$$X_{7} = \begin{pmatrix} V_{1} \\ I_{1} \end{pmatrix} | L_{1} \end{pmatrix} | L_{1}$$

$$X_{7} = \begin{pmatrix} V_{1} \\ I_{1} \end{pmatrix} | L_{1} \end{pmatrix} | L_{1}$$

$$X_{7} = \begin{pmatrix} V_{1} \\ I_{1} \end{pmatrix} | L_{1}$$

$$X_{7} = \begin{pmatrix} V_{1} \\ I_{1} \end{pmatrix} | L_{1} \end{pmatrix} | L_{1}$$

$$X_{7} = \begin{pmatrix} V_{1} \\ I_{1} \end{pmatrix} | L_{1} \end{pmatrix} | L_{1}$$

$$X_{7} = \begin{pmatrix}$$

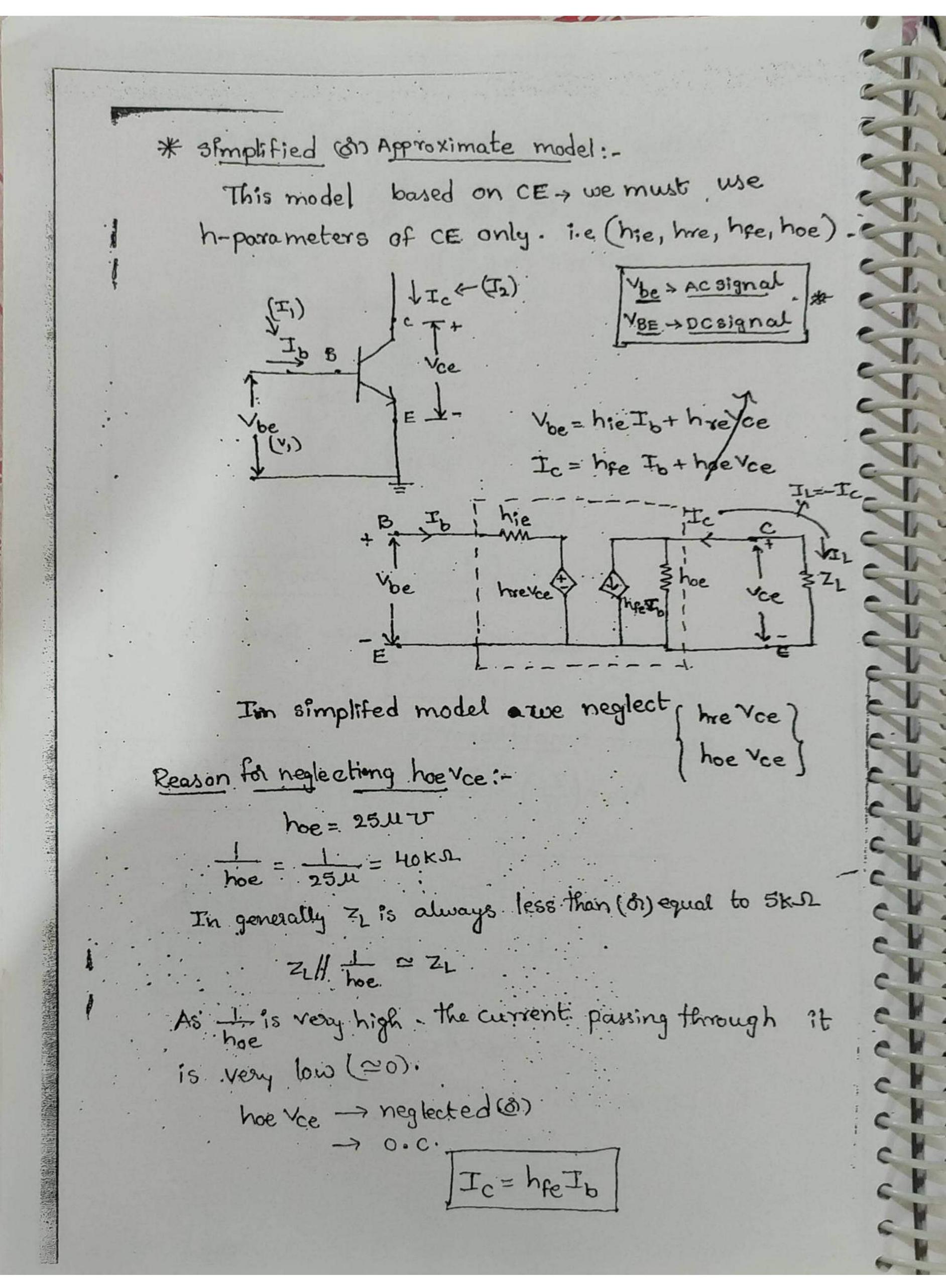

Procedure to draw the Ac equivalent ext of a given

1. Replace the transister by its equivalent simplified model

2. Connect the Ckt components at common , 1/p 4 0/p

terminal.

in connect the resistors directly.

(ii) when freq of signal 4 cap values one given, calculate the reactance of each capacitor.

if Xc → Veryhigh => All the c' are replaced by o.c.

Xc -> very low => c' are replaced by s.c.

(iii) when freq of signal (di) capacitance value not given all the apacitors are replaced by s.c.

3. All the DC sources are set equal to zero in the AC equivalent. ckt.

-68

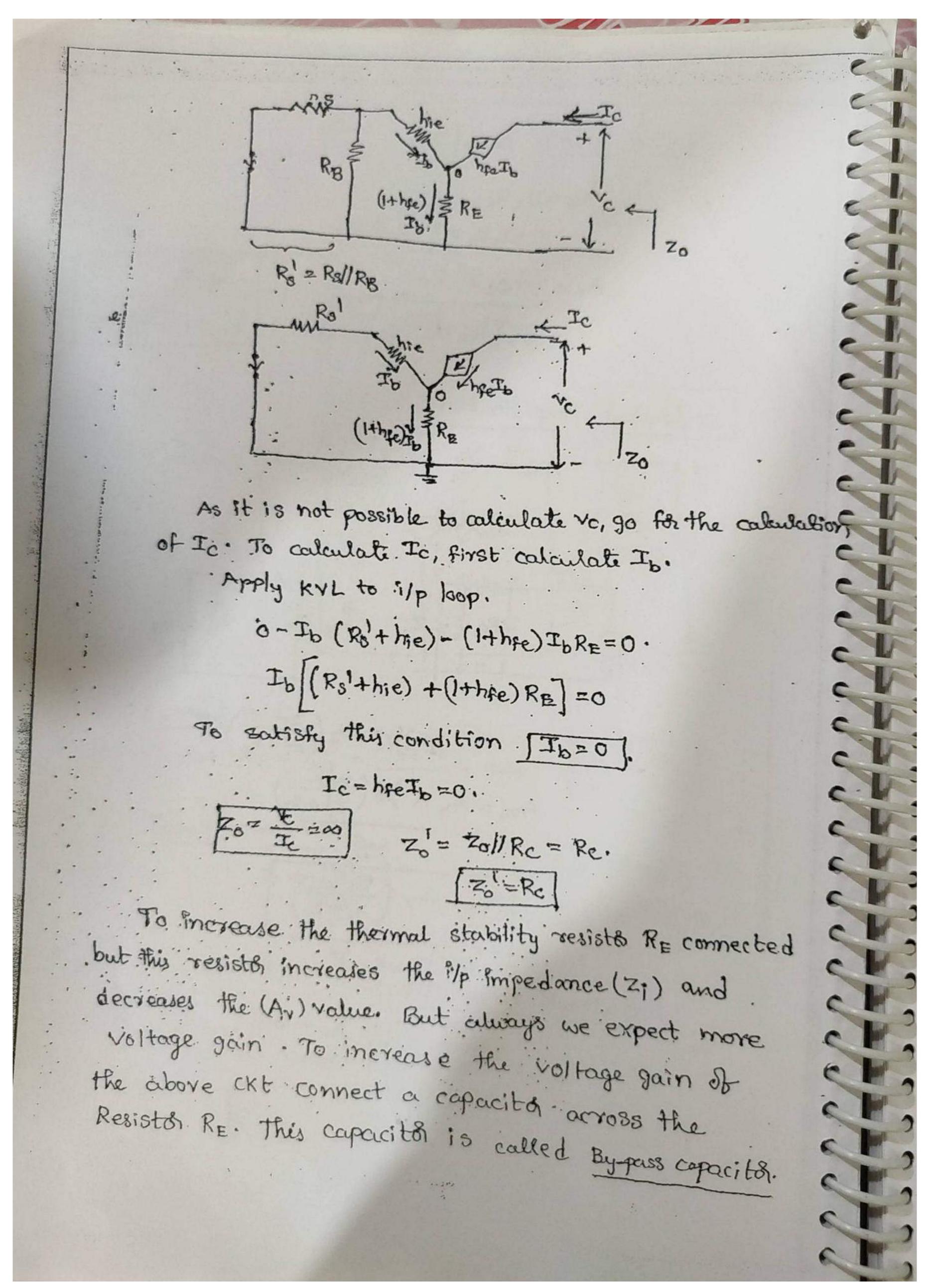

As It is not possible to calculate Vc, go for the calculation of Ic. To calculate Ic, first calculate Ib.

Apply KVL to ilploop

0-Ib(Rs+the)=0.

Ib (Rs+hie) =D

To satisfy this condition,

Jb=0

Ic=hgeIb= 0.

$\Rightarrow \overline{Z_0 = \frac{V_C}{T_C} = \infty}$

> Z' = Zo// Rc

= Rc Zo = Reserve Rc Z6 Rc+Zo = Rc+Zo

= Rc.1

: | Zo = Rc

\* As there is no Revistor in RE in the above ckt its stability factor (I+B) this ckt is thormally less starts increase the thormal stability a resistor RE connected at emitter this revistor decreases the stability factor and increases the thermal stability.

Scanned by TapScanner

Scanned by TapScanner

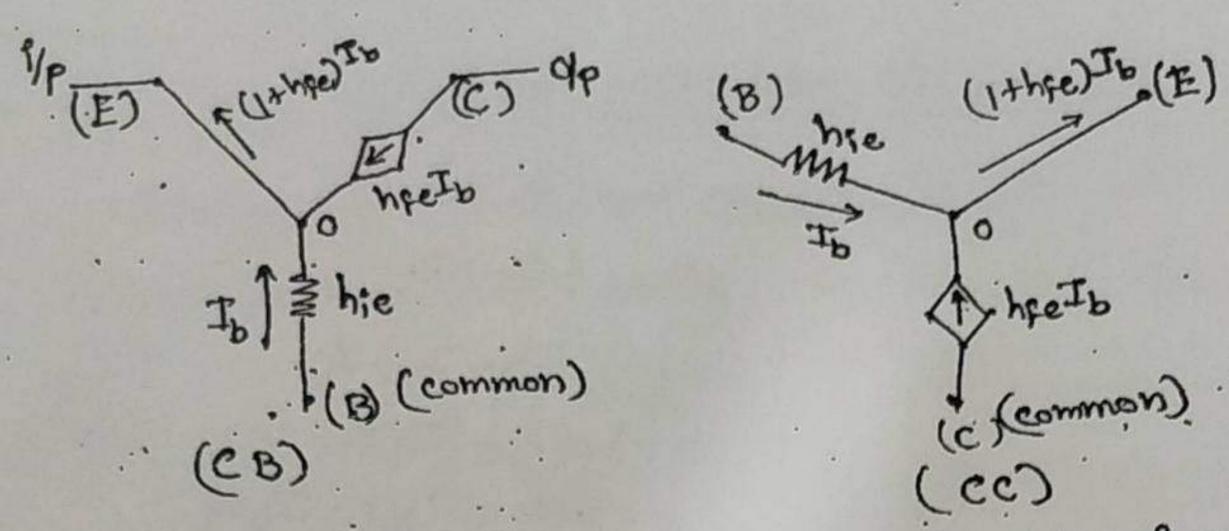

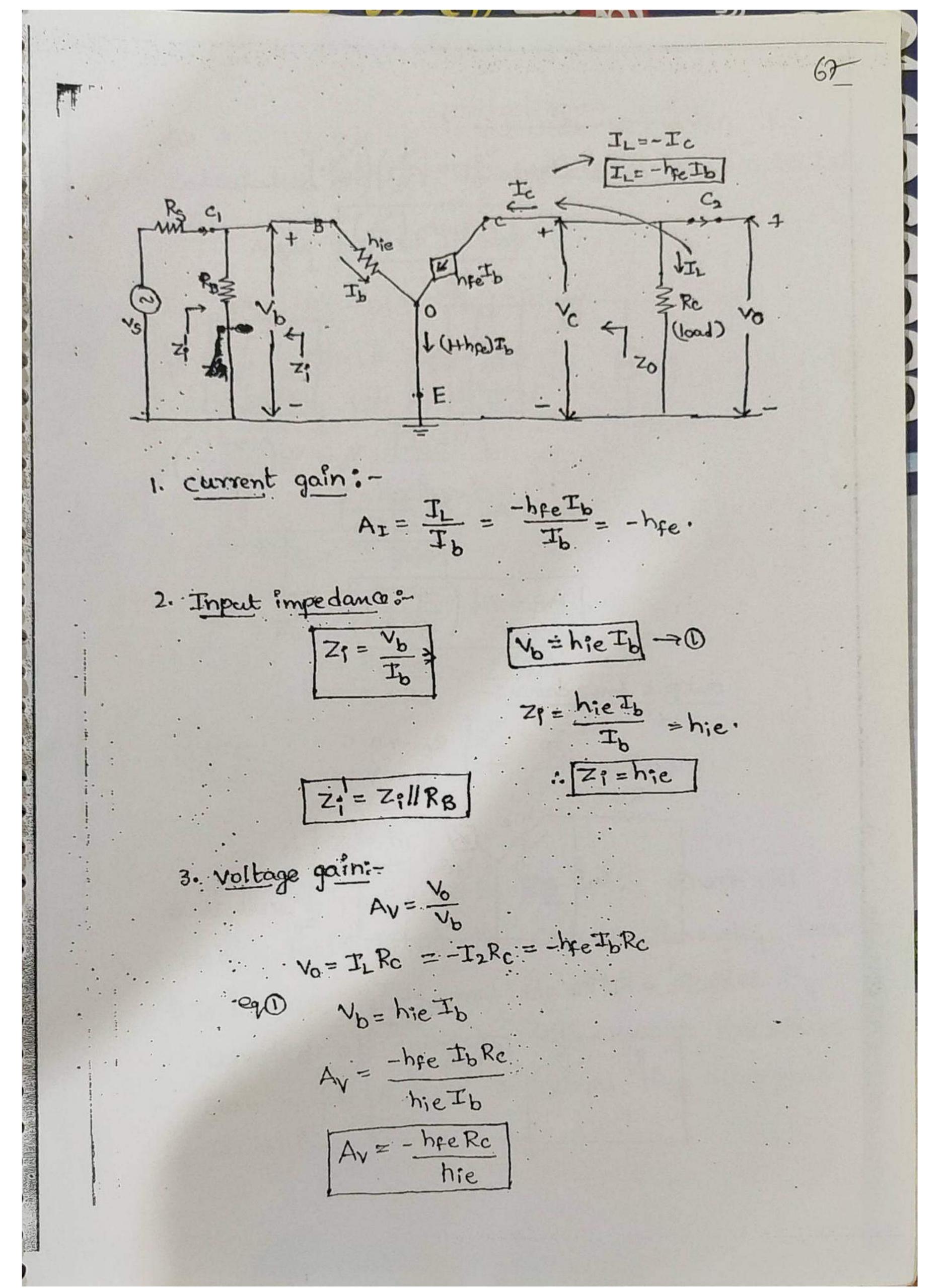

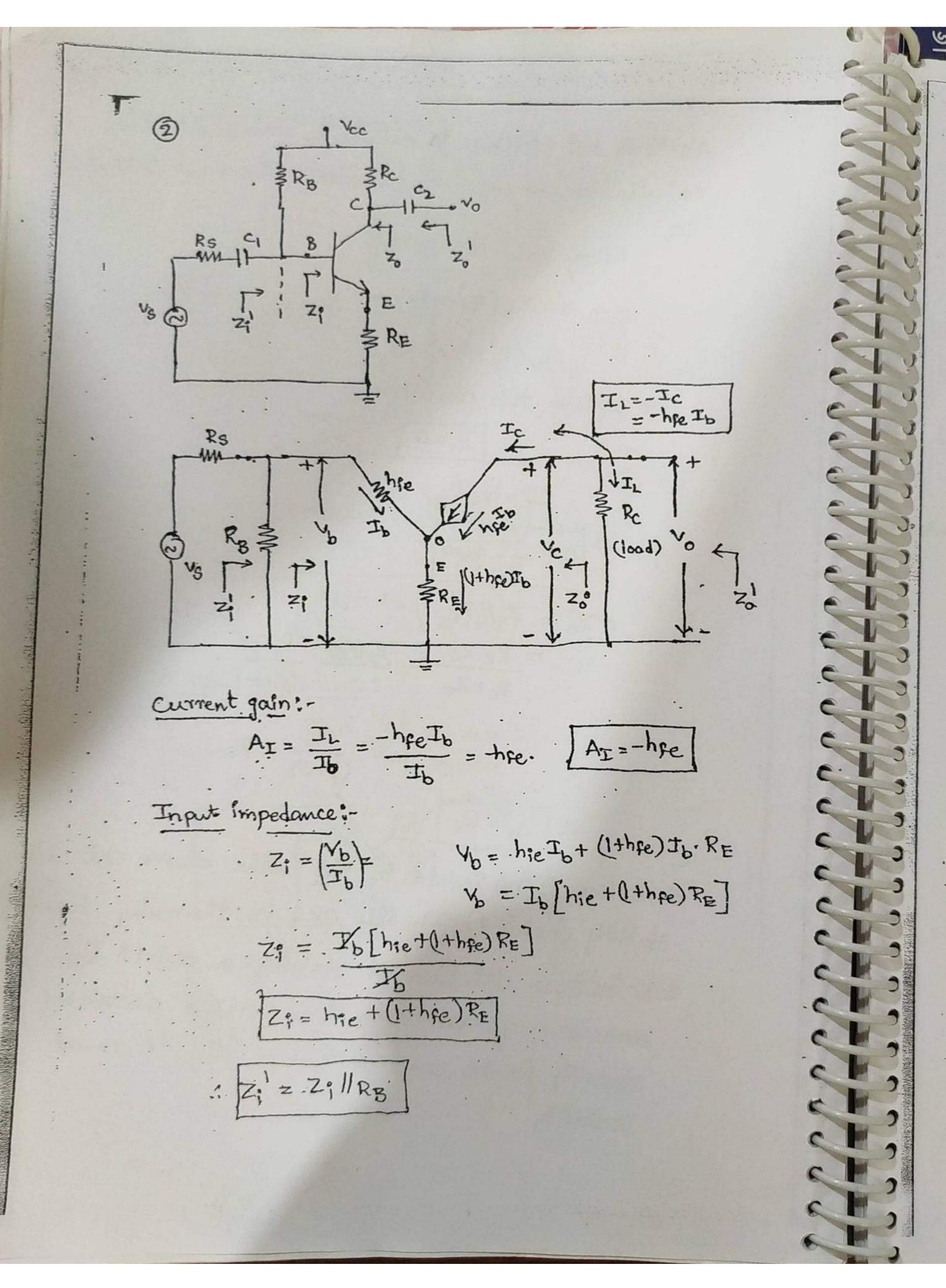

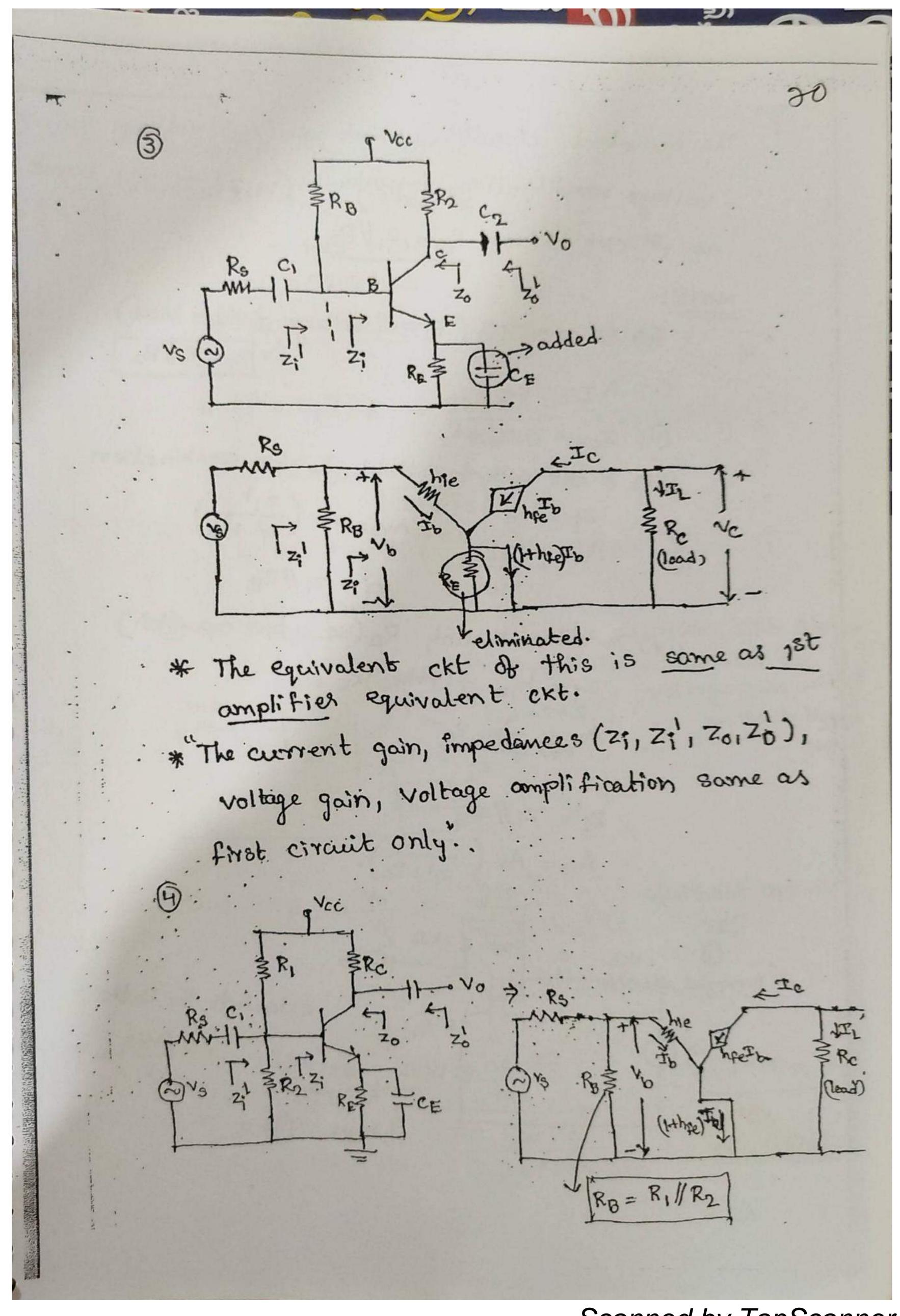

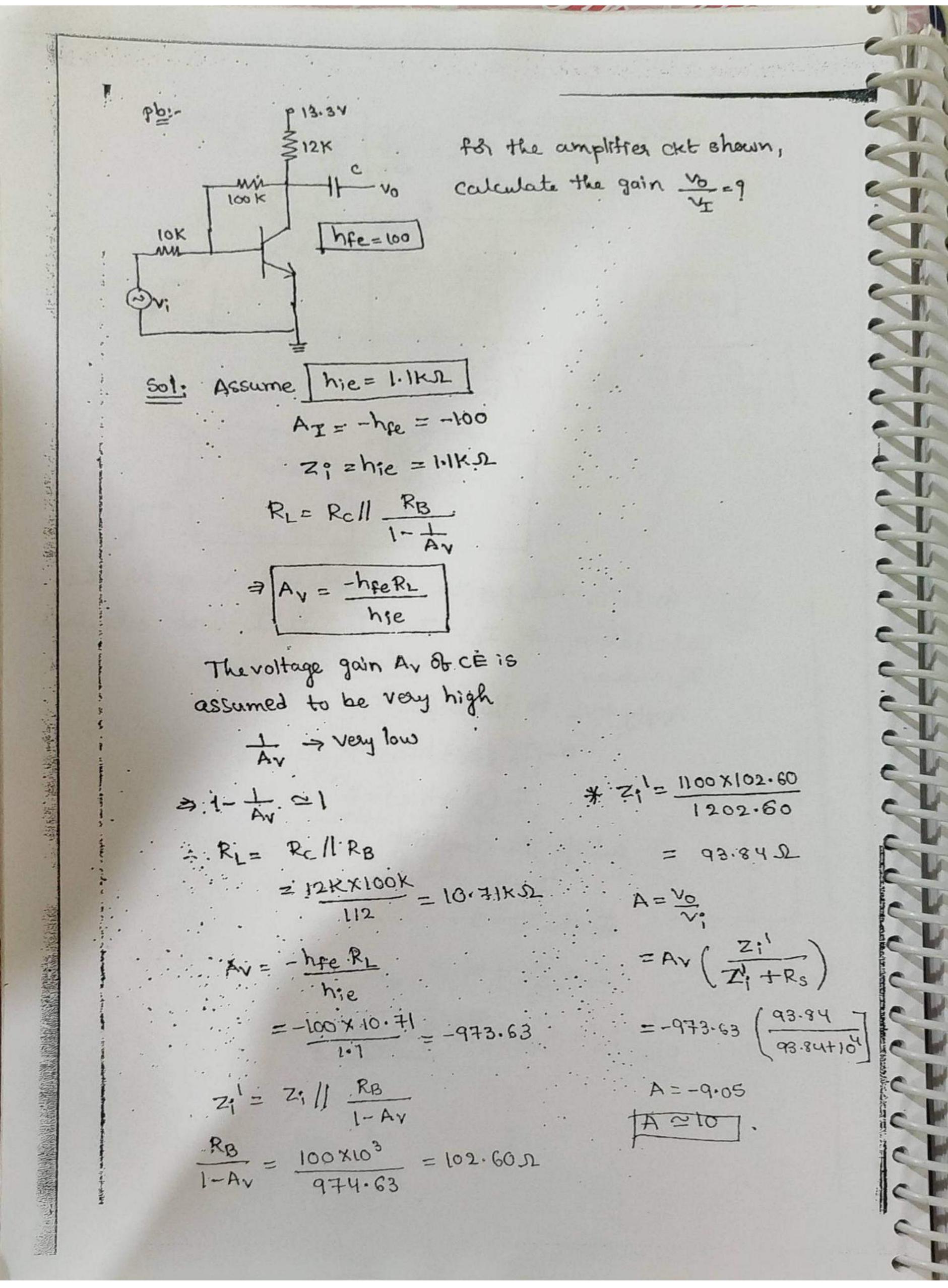

Current gain:

$$A_{I} = \frac{T_{L}}{T_{b}} = \frac{-h_{fe}T_{b}}{T_{b}} - h_{fe}.$$

$$T_{I} = \frac{V_{b}}{T_{b}} = \frac{h_{ie}T_{b}}{T_{b}} = h_{ie}.$$

$$Z_{1} = \frac{V_{b}}{T_{b}} = \frac{h_{ie}T_{b}}{T_{b}} = h_{ie}.$$

$$Z_{1} = h_{ie}$$

$$V_{b} = T_{b}h_{ie}$$

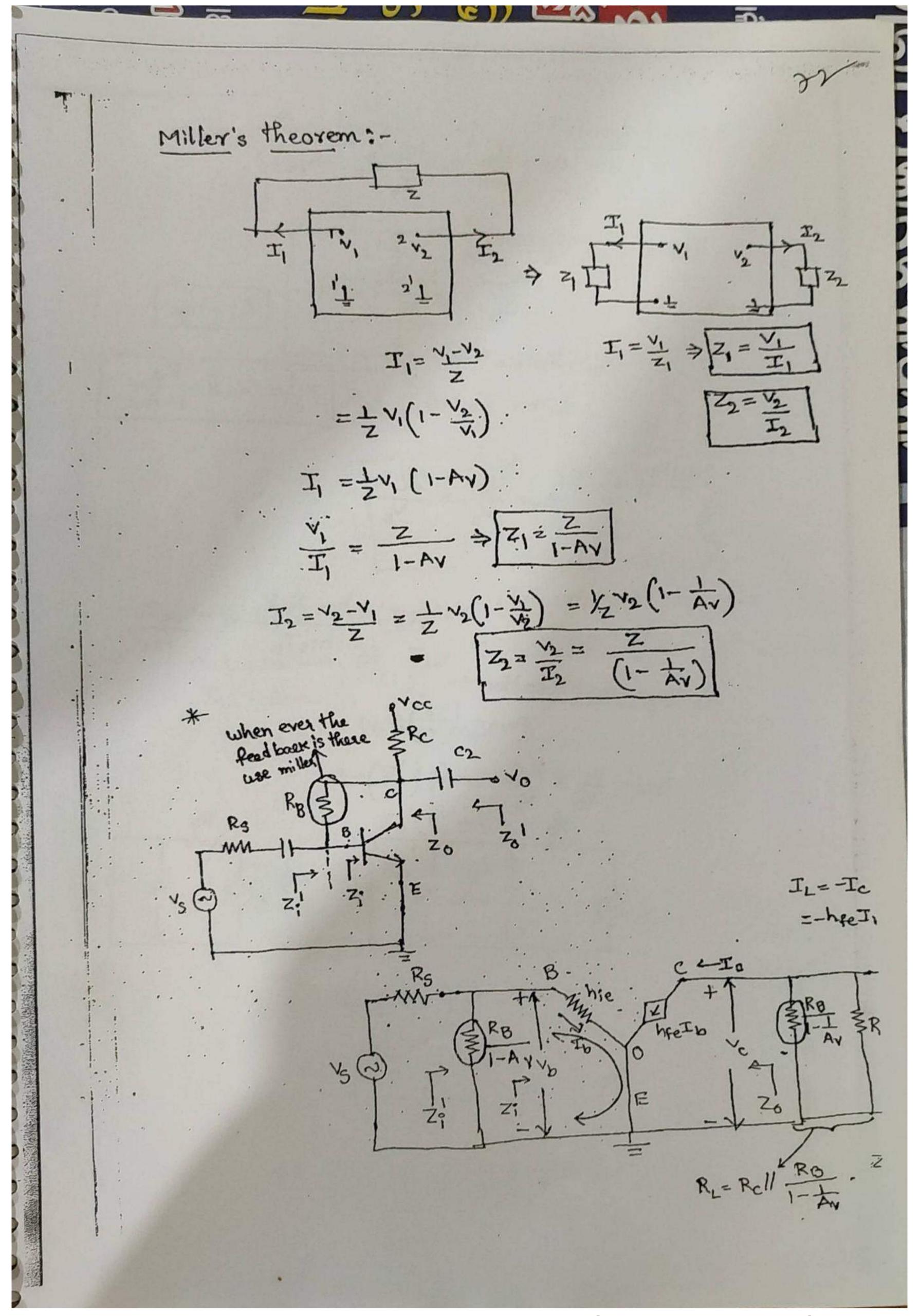

$$Z_{1} = Z_{1} \parallel \frac{R_{0}}{I - A_{V}}$$

$$V_{b} = I_{b}R_{b}$$

$$V_{b} = I_{b}R_{b}$$

$$V_{b} = h_{fe}T_{b}R_{b}$$

$$V_{b} = V_{b} \times \frac{V_{b}}{V_{b}} = A_{V}(\frac{V_{b}}{V_{b}})$$

$$A_{V_{b}} = V_{b} \times \frac{V_{b}}{V_{b}} = A_{V}(\frac{V_{b}}{V_{b}})$$

$$A_{V_{b}} = A_{V}(\frac{V_{b}}{Z_{1}^{1} + R_{b}})$$

$$A_{V_{b}} = A_{V}(\frac{V_{b}}{Z_{1}^{1} + R_{b}})$$

$$A_{V_{b}} = A_{V}(\frac{V_{b}}{Z_{1}^{1} + R_{b}})$$

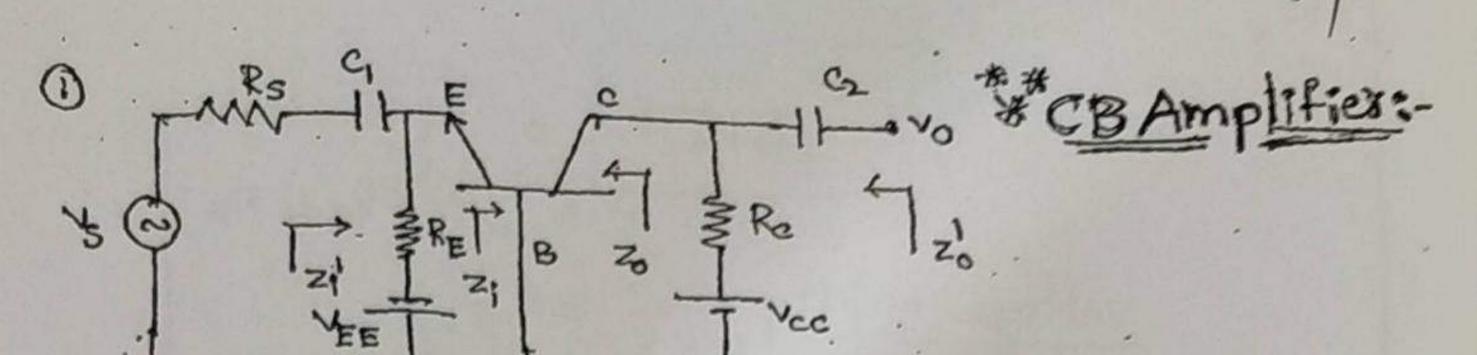

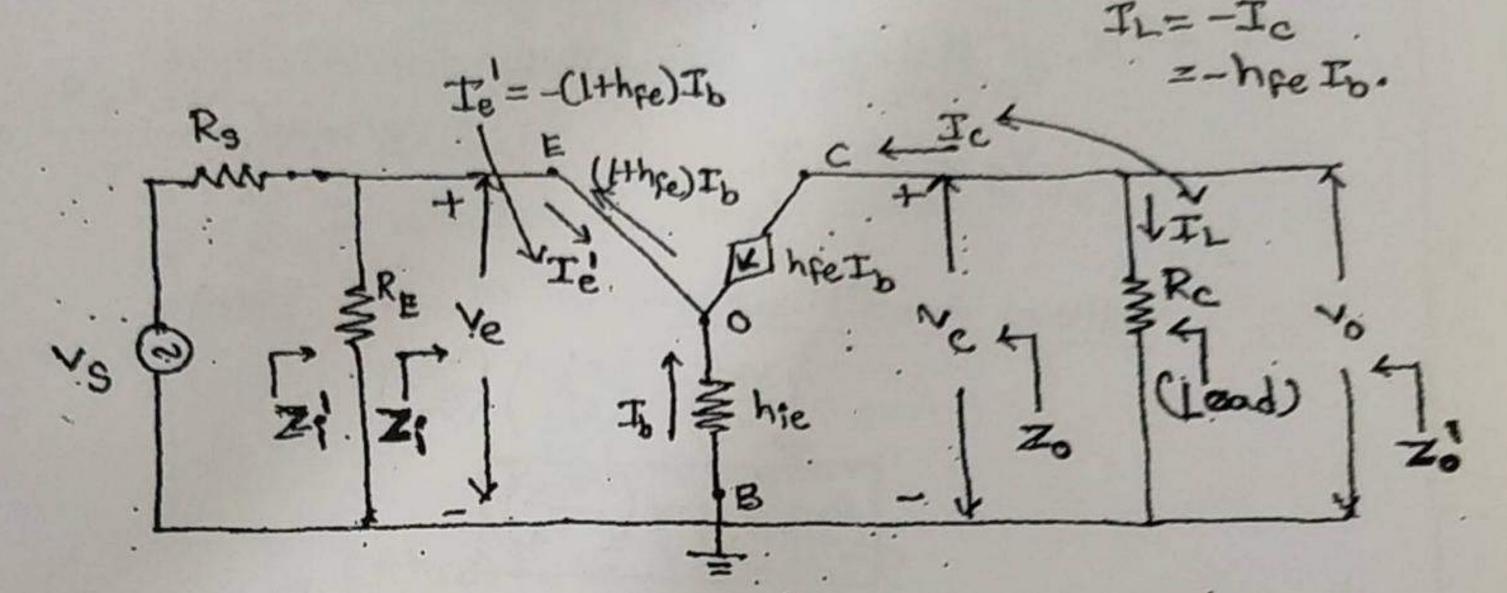

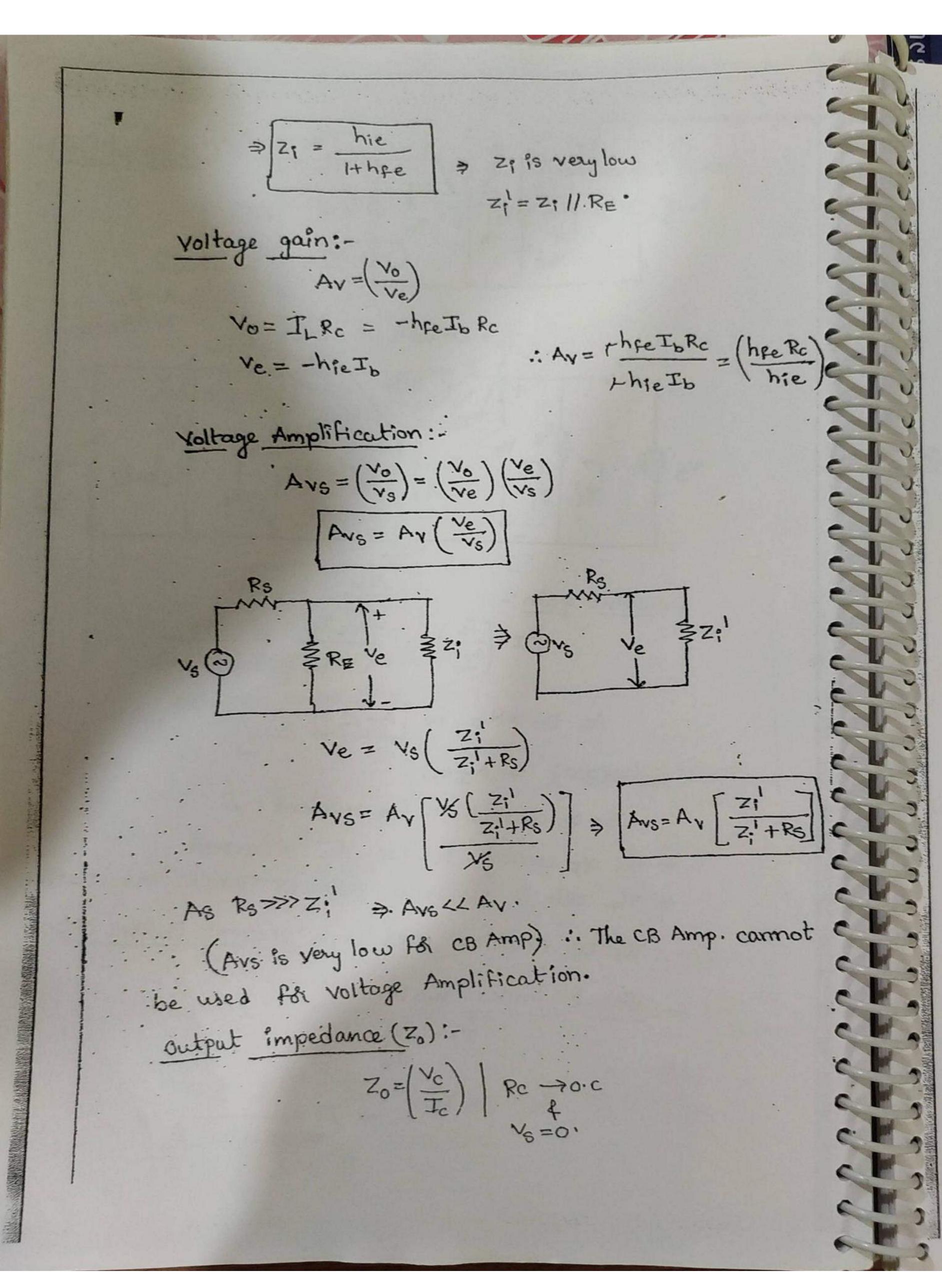

$$A_{I} = \left(\frac{T_{L}}{T_{e}^{'}}\right) = \frac{-h_{fe}T_{b}}{-(1+h_{fe})T_{b}} = \frac{h_{fe}}{(1+h_{fe})}$$

The op current ~ 1/p eurient.

\* The olp current follows the ilp current.

\* The cit is current follower (8) current Buffer

... The CB. Amplifier used as a current Buffer Ckt.

$$Z_1 = \frac{\sqrt{e}}{T_e}$$

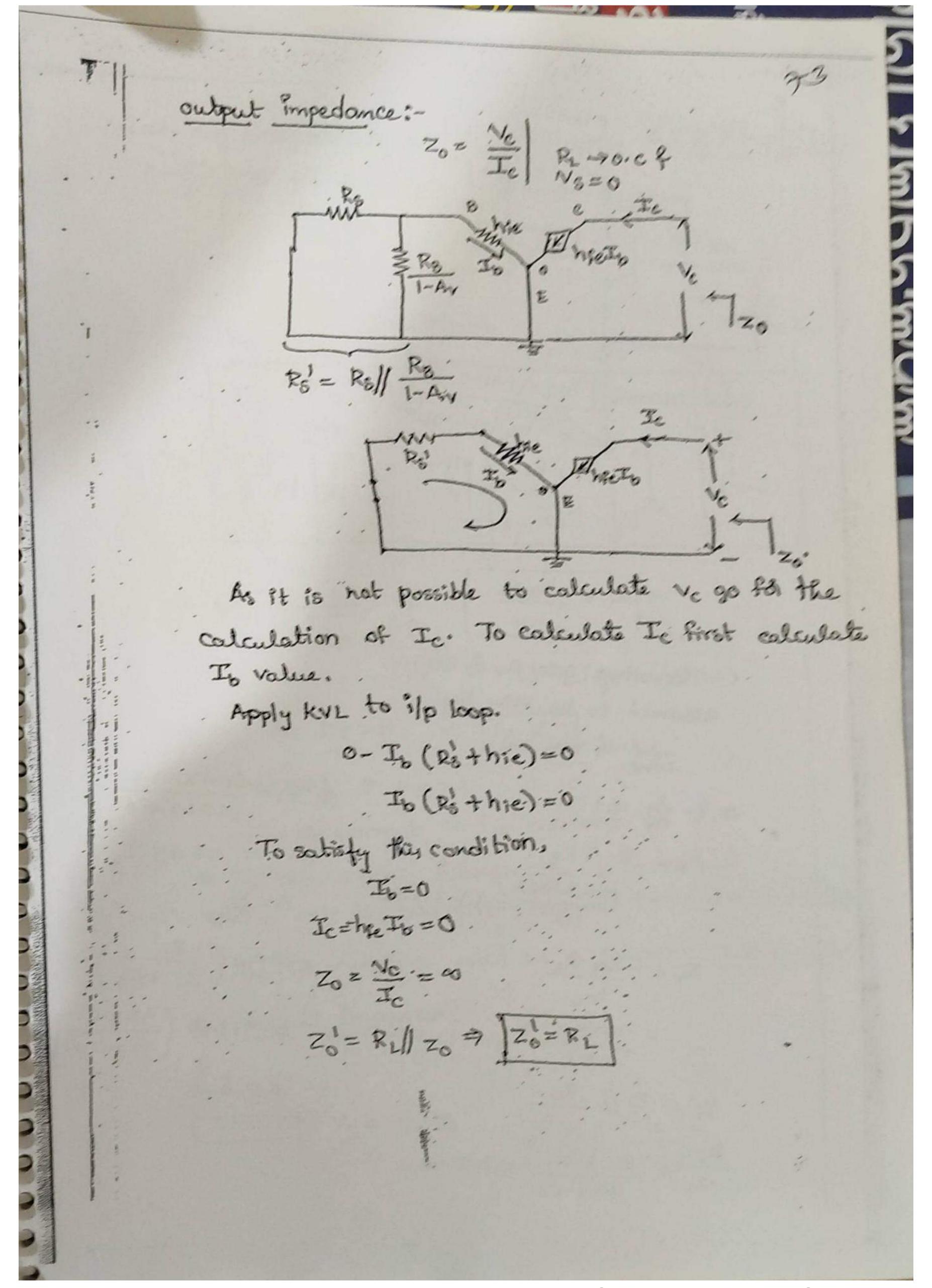

As it is not possible to calculate 16,90 for the calculation of Ic.

To calculate Ic, first calculate Ib.

APPLY KUL to ilp loop:

To satisfy the condition.

# CB Amplifier can't used for voltage amplification

& current amplifion. It is only used for appurrent

= ilp current.

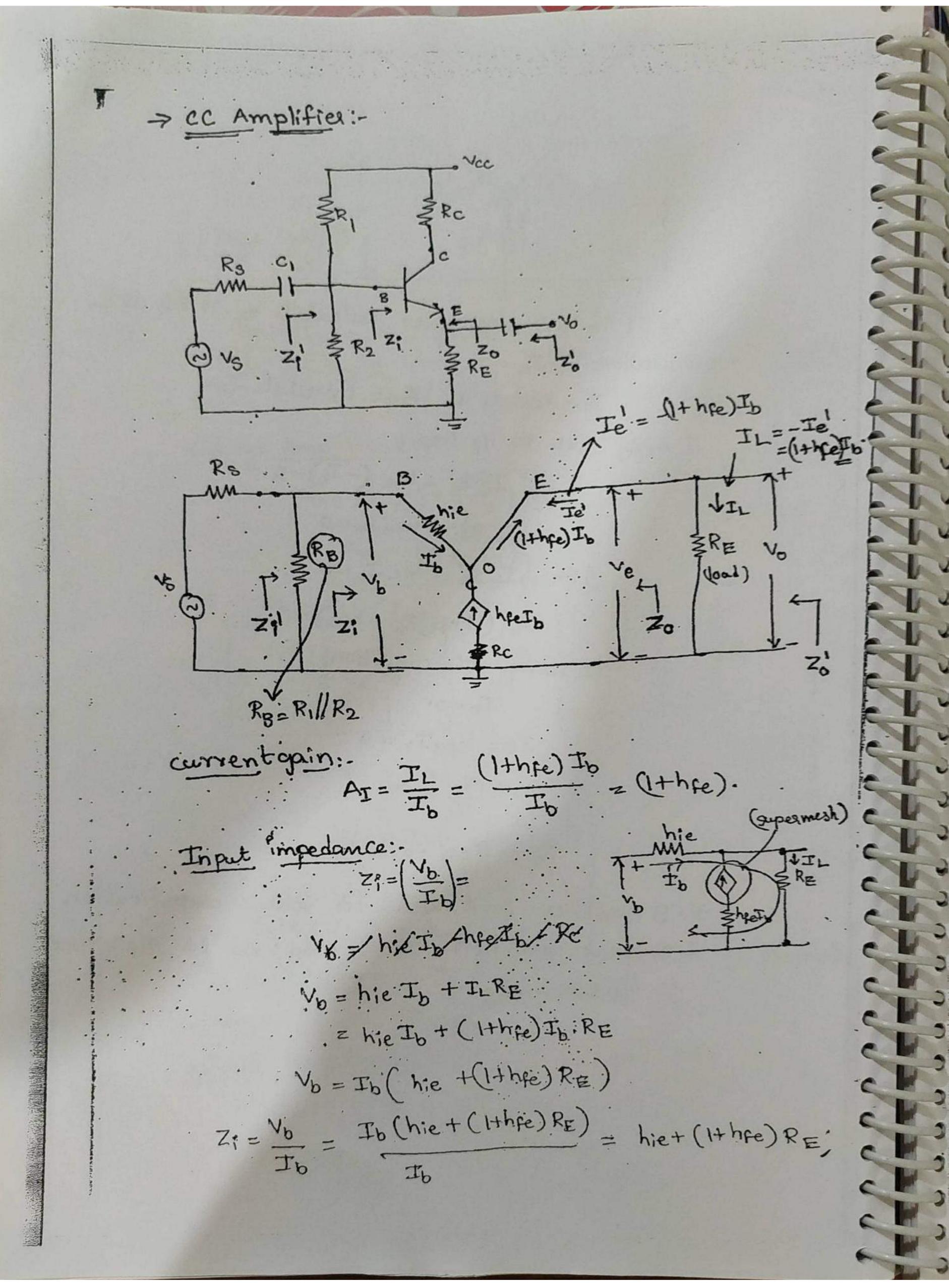

Voltage gain (Av) =

$$\frac{V_0}{V_b}$$

.

$V_0 = ILR_E$ .

$A_V = \frac{V_0}{V_0}$

$V_0 = (1+hfe)I_bR_E$ .

The olp voltage follows the ilp voltage.

-> voltage-follower ckt (OR)? voltage Buffer. ckt (8)

Emitter follower ckt

\* cc Amplifier used as voltage Buffer ckt..

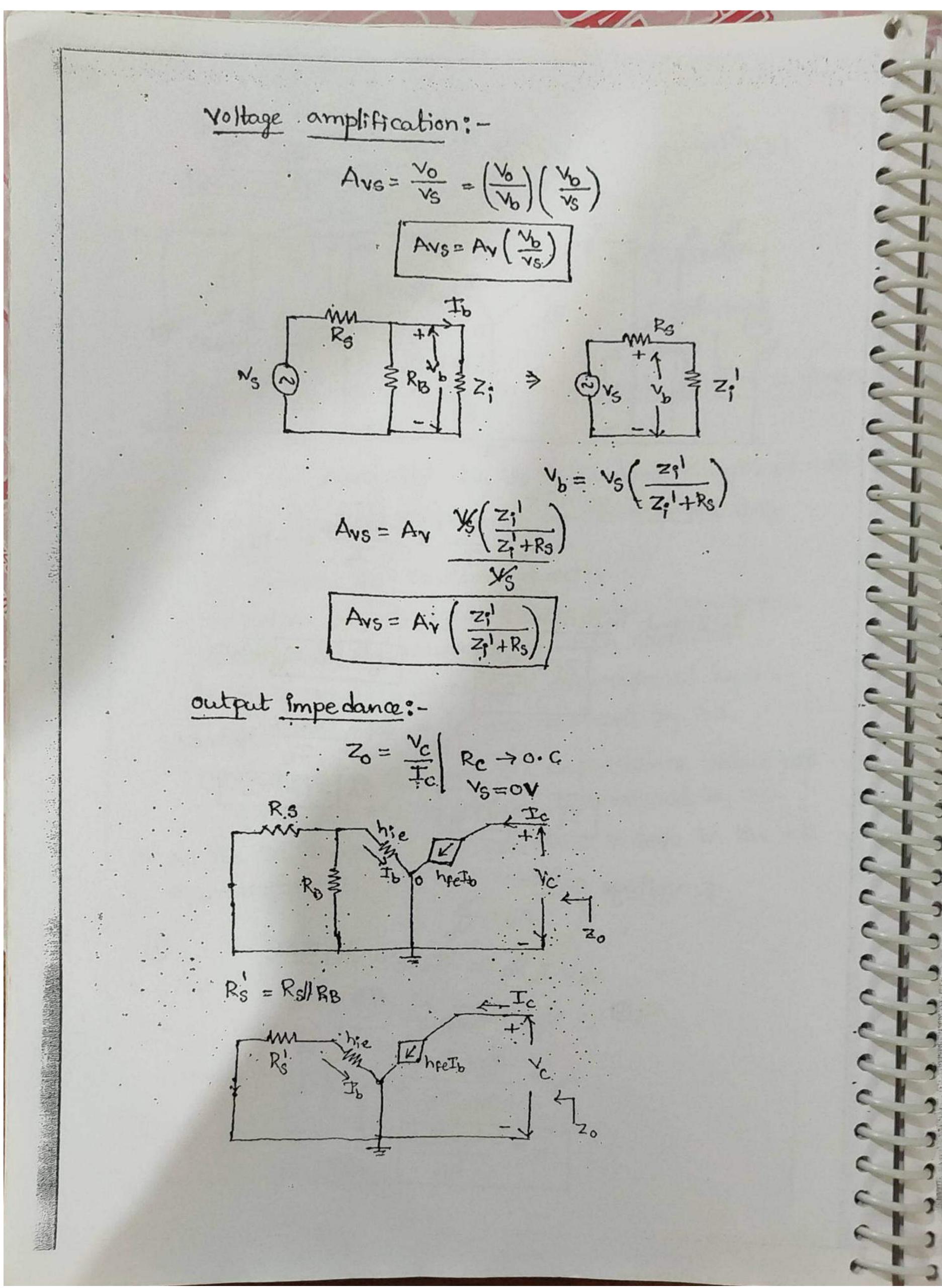

voltage Amplification:-

Avs =

$$\frac{V_0}{V_8} = \left(\frac{V_0}{V_b}\right) \left(\frac{V_b}{V_s}\right) \Rightarrow Avs = Av \left(\frac{V_b}{V_s}\right)$$

$$V_b = V_S \left( \frac{Z_1^{\prime \prime}}{Z_1^{\prime \prime} + R_S} \right)$$

$$A_1 \left( \frac{V_b}{V_b} \right) = A_1 \left( \frac{Z_1^{\prime \prime}}{Z_1^{\prime \prime}} \right)$$

$$Av_6 = Av\left(\frac{v_b}{v_s}\right) = Av\left(\frac{Z_1'}{Z_1' + Rs}\right)$$

=1- <1 (8) Av<1 > Av<1 ... cc Amplifier, connot be used for voltage complifican 1 output impedance (20):-Ve= - Ib (hie+Rs) Ie'= - (1thfe) Ib. : Zo= +Ib( hie + Rs) Zo > very low for cc amplifier +(I+hfe)Ib | Zo = Zo//RE F& CE amplifies:-\* Among these 3' the CE is only used for amplification. \* For CE amplifier is most préférable used amplifier. \* for CE ampliffer (i) Zi=hie -> very low. (ii) Zo = 00 - very high. ("iii) Ay = -hfeRc -> very high. The expected values from the amplifier are ii) Av -> very high - (more amplification). (ii) Z: -> very high - 1 driving capacity of ckt of Power dissipation in the

(iii) Zo-Verylow - I the loading effect on 1/p signal \* As we compare the CE amplifier values with the expected values from the amplifier the CE amplifier hot satisfying the impedance chara so there is a necessity to improve the Impedance once characteristics ( ipimpedance, I op impedance. \* As the collector collecting the charged posticles, the temperature across the junction To increases.

AS T1 >> heet, Av1 but the gain of amplifies must be constant.

But as temp 1, Av 1 for CE amplifier in this CE amplifier suffers from stability problem. There is a necessity to increase the thermal stability. To 1 thermal stability of To 1 improve the impedan characteristics negative feed back employed.

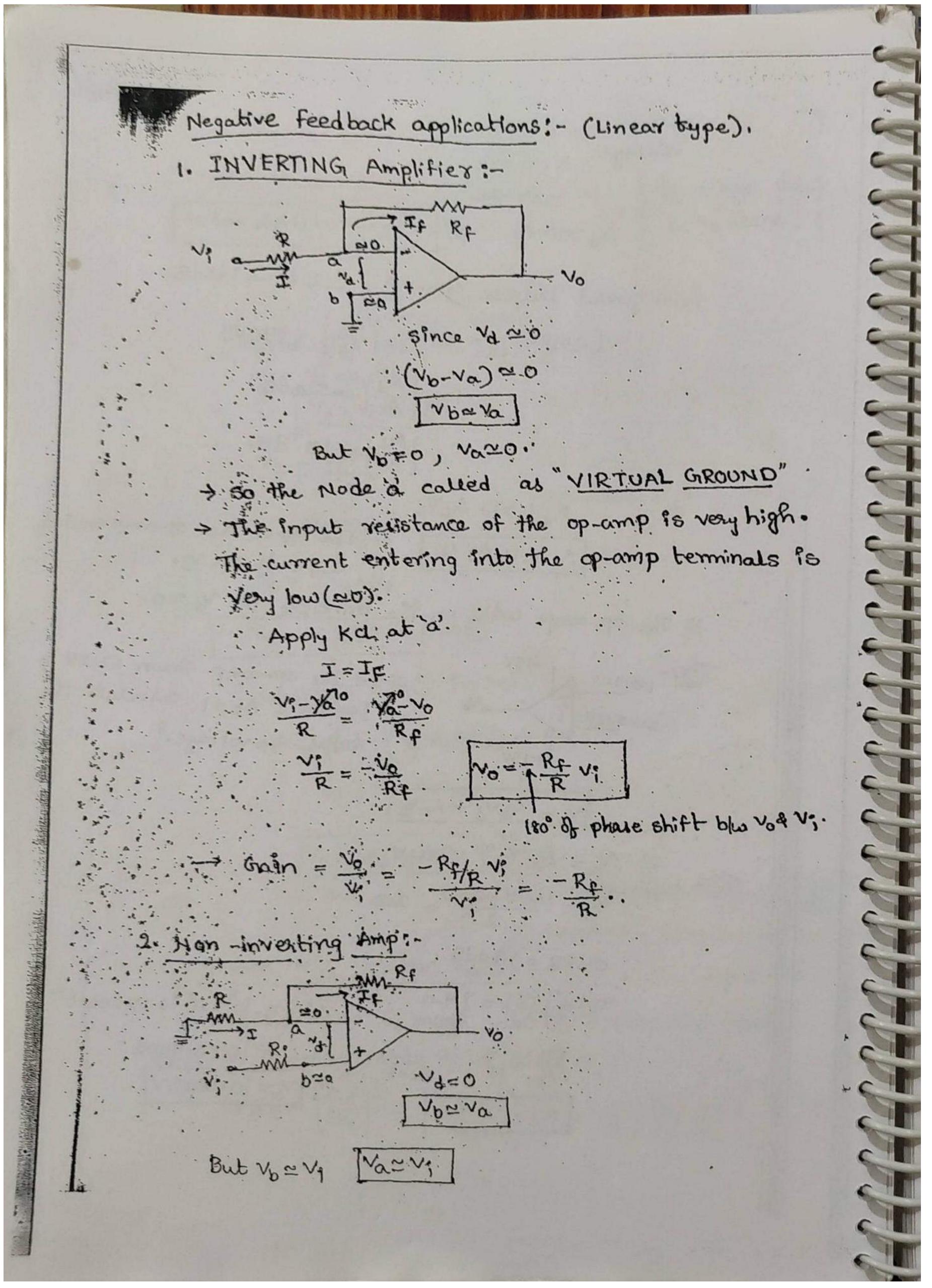

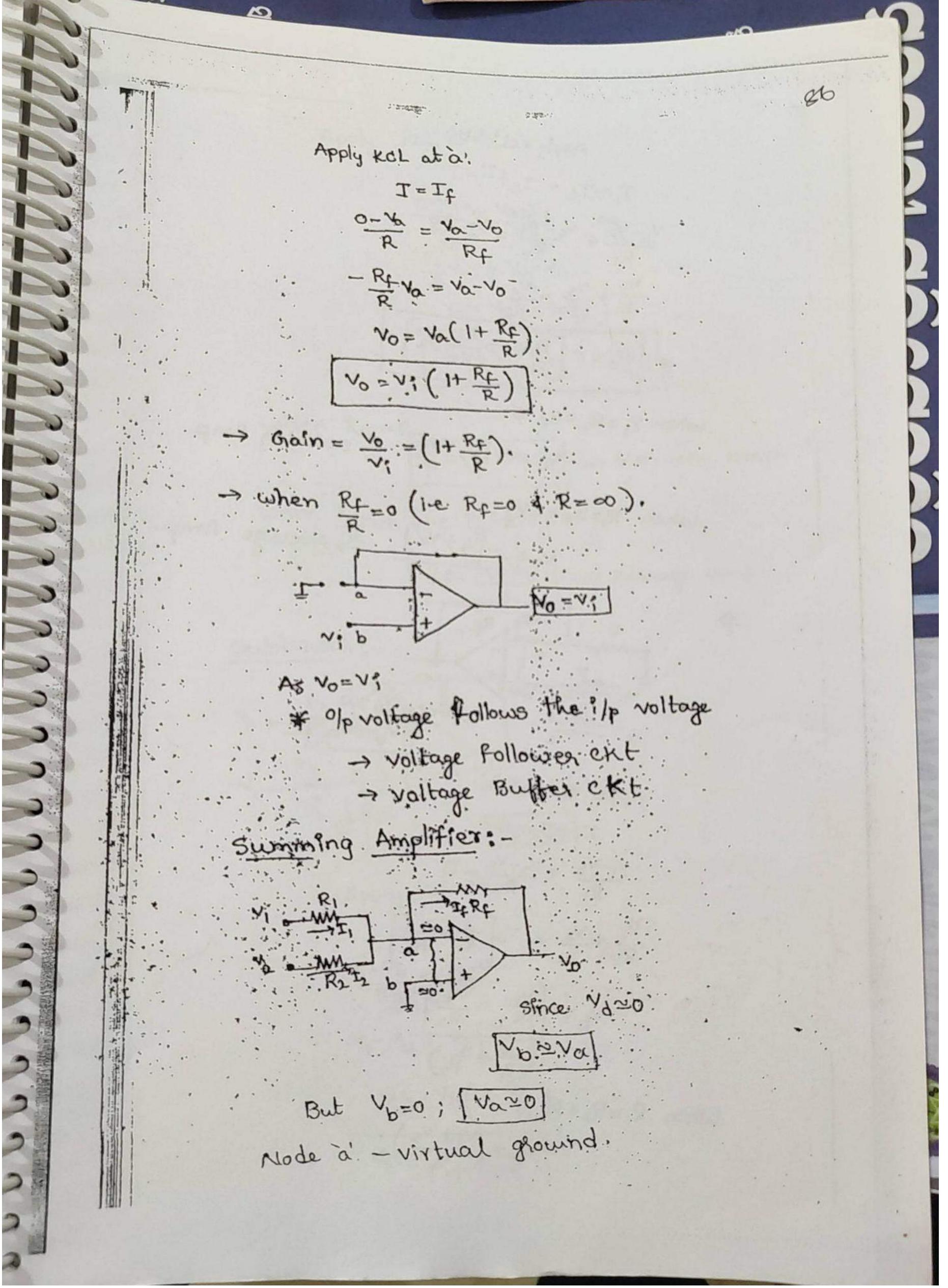

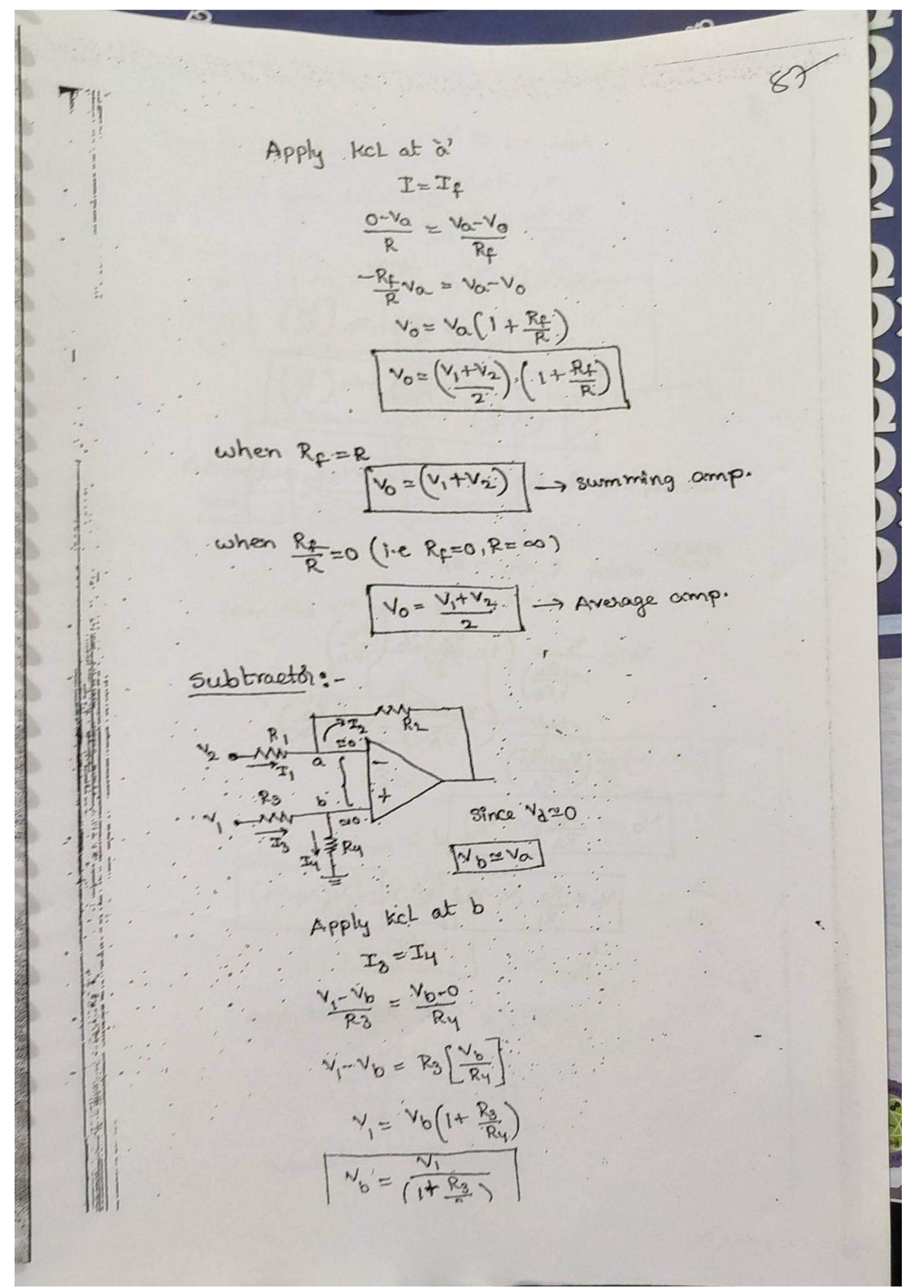

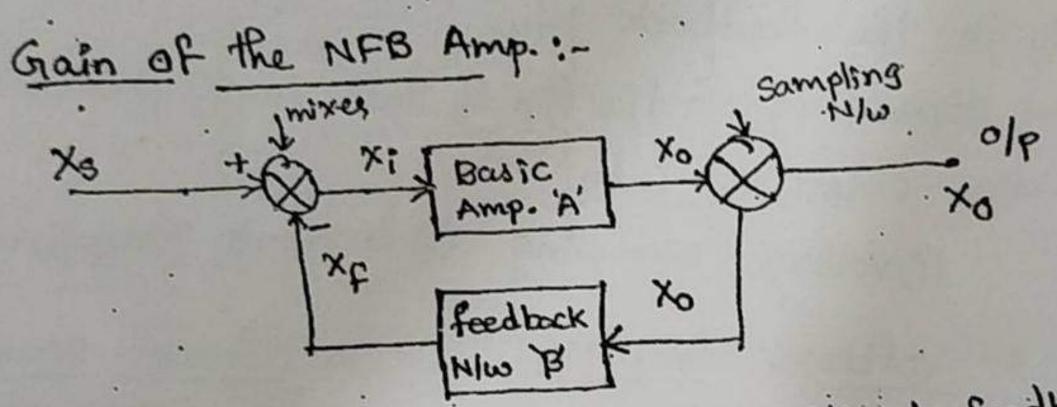

# Negative Feedback Amplifiers:-Block diagram: X0] 7\_ Xo 2. Mixing N/w:-This N/w combines the signals coming from source of feedback : N/w. \* In they feed back Amp. the mixer is a differential X: = X 5-XC \* Depending on mixing of signals, the mixing n/wis are classified into 1. Beries mixer:-2. Shunt mixer:we mix the voltage signals : we mix current signals in parallel Source B-A porallel to

Source,

.W/w.

in series

gowice

Series mixer

#### 3. Basic Amplifier: -

Depending on the ilp & olps of the Basic amp, they classified into:

- 1. Voltage amplifier,  $Av = \left(\frac{V_0}{V_i}\right)$

- 2. Current Amplifier,  $A_{I} = \left(\frac{I_0}{I_1}\right)$

- 3. Frans resistance Amplifier,  $R_m = (\frac{V_0}{T_1})$

- 4. Troons conductance Amplifies, Gm= (To)

#### 4. 3ampling N/w:-

This now connects the opp of Basic amplifier as ip to the feedback Nlw

- Depending on the ofp of Basic Amp. the sampling N/u are classified into .

Ovoltage sampling @current sampling.

1- voltage sompling:

B. A val voltage

B. A val voltage

Shunt

Sompling

Nilw vo

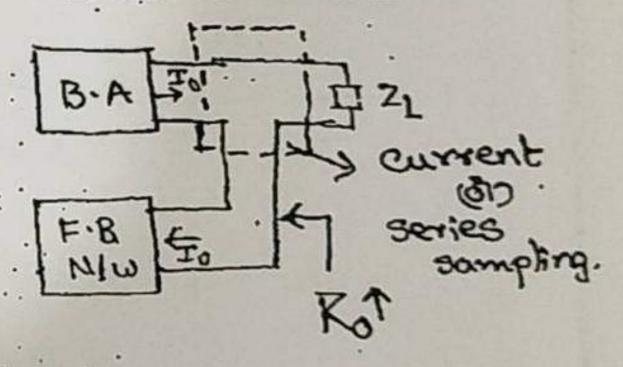

2. current sampling:-

- 5. Feedback N/w:- A part of the B.A Olp is given as ilp

to the Basic Amplifier through feedback N/w. This

n/w reduces the signal strength. This n/w also called

Attenuat & N/w.

- This n/w consists only Resistas.

where  $\beta = \frac{\chi_{f}}{\chi_{0}}$ ,  $\chi_{f}(\chi_{0}) \Rightarrow \beta(1) \Rightarrow [0 < \beta < 1]$

R\_s P\_ 12 \_ 12 \_ 12 Factor (31) Ratio Attenuation factor (32)

Retransmission factor & Ratio.

\* Depending on sampling N/w & Mixing N/w, the NFB Amplifier are classified into:

III voltage - series (OR) shunt - series NFB Amp.

Most preknowly.

Rod R: 1 ...

2. Voltage - Shunt (OR) Shunt-Shunt NFB Amp.

3. current - series (OR) series - series NFB Amp.

14] current - shunt (OR) series - shunt NFB Amp. least. xRot. Rilx

A -> Grain of the complified without feedback  $A = \left(\frac{x_0}{x_0}\right)$

B-> feedback factor, B= Xf xo, B<1

Af -> Grain of the amp. with feed back

With feed back  $x_i = x_s - x_f$

$$x_0 = A(xs-xf)$$

$$= Axs - Axf$$

$$= Axs - A(Pxo)$$

$$x_0(1+\beta A) = A x_S$$

$$\frac{x_0}{x_S} = Af = \frac{A}{1+\beta A}$$

Por NFB Amp, (1+BA)>1

### AfKA

\* The gain with feedback reduced by a factor of (I+BA).

\* The reduced gain -> 1 the Btability.

-> 1 the Bound width.

-> I the Hoise.

-> I the distribun.

## \* The general char of NFB Amplifiers: -

- L. stability more

- 2. Increased Boundwidth

- 3. pecreased Noise

- 4. Decreased Distortion

- 5. i/p& ofp resistances changes appreciably depends on type of feedback.

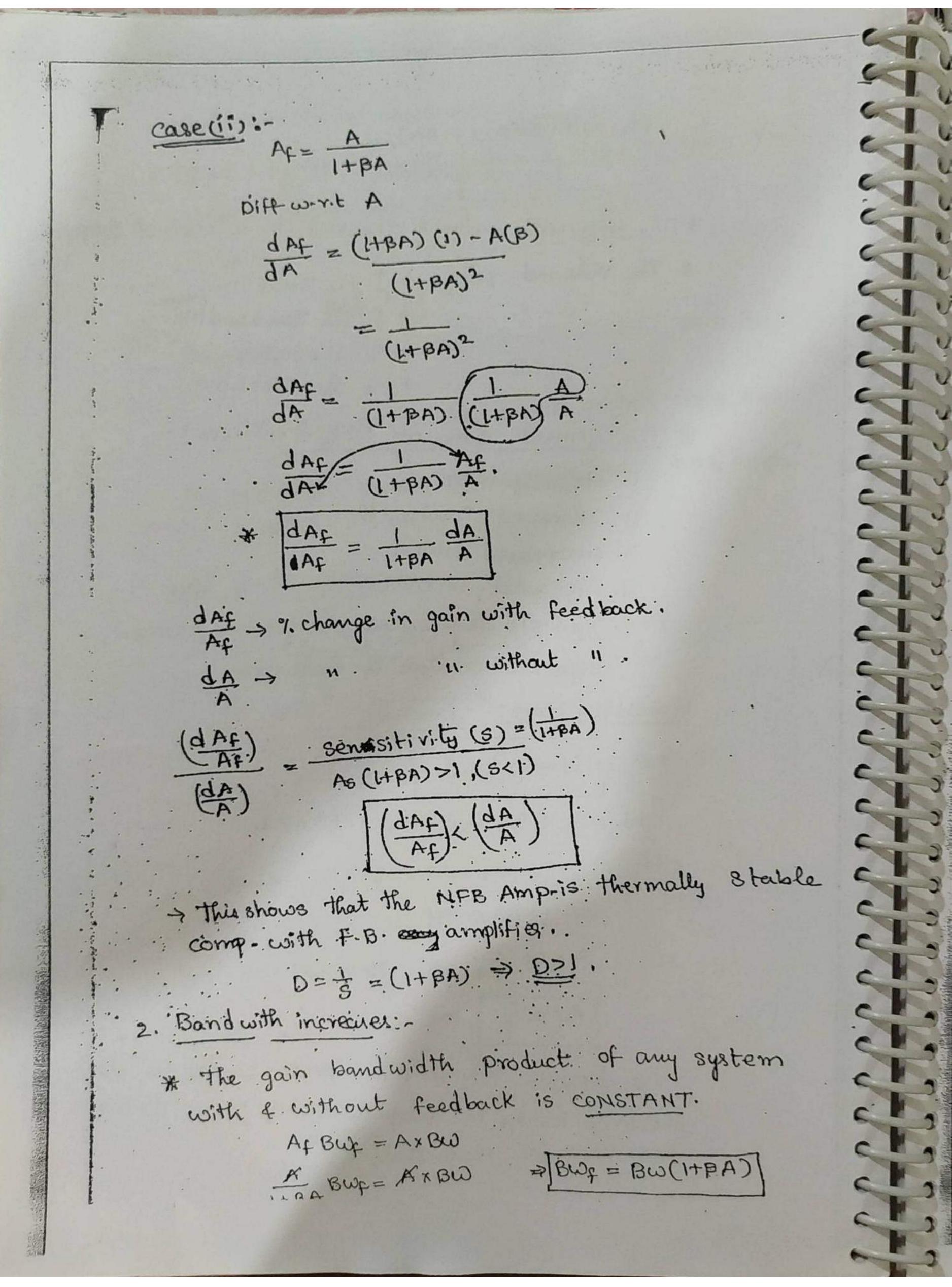

1- stability More: -

$$Af = \left(\frac{A}{1+BA}\right)$$

for Neg F.B amplifier, (1+BA)>1.

Case(i): (i+ pA) -> veryhigh.

1+BA~ BA.

At ~ X

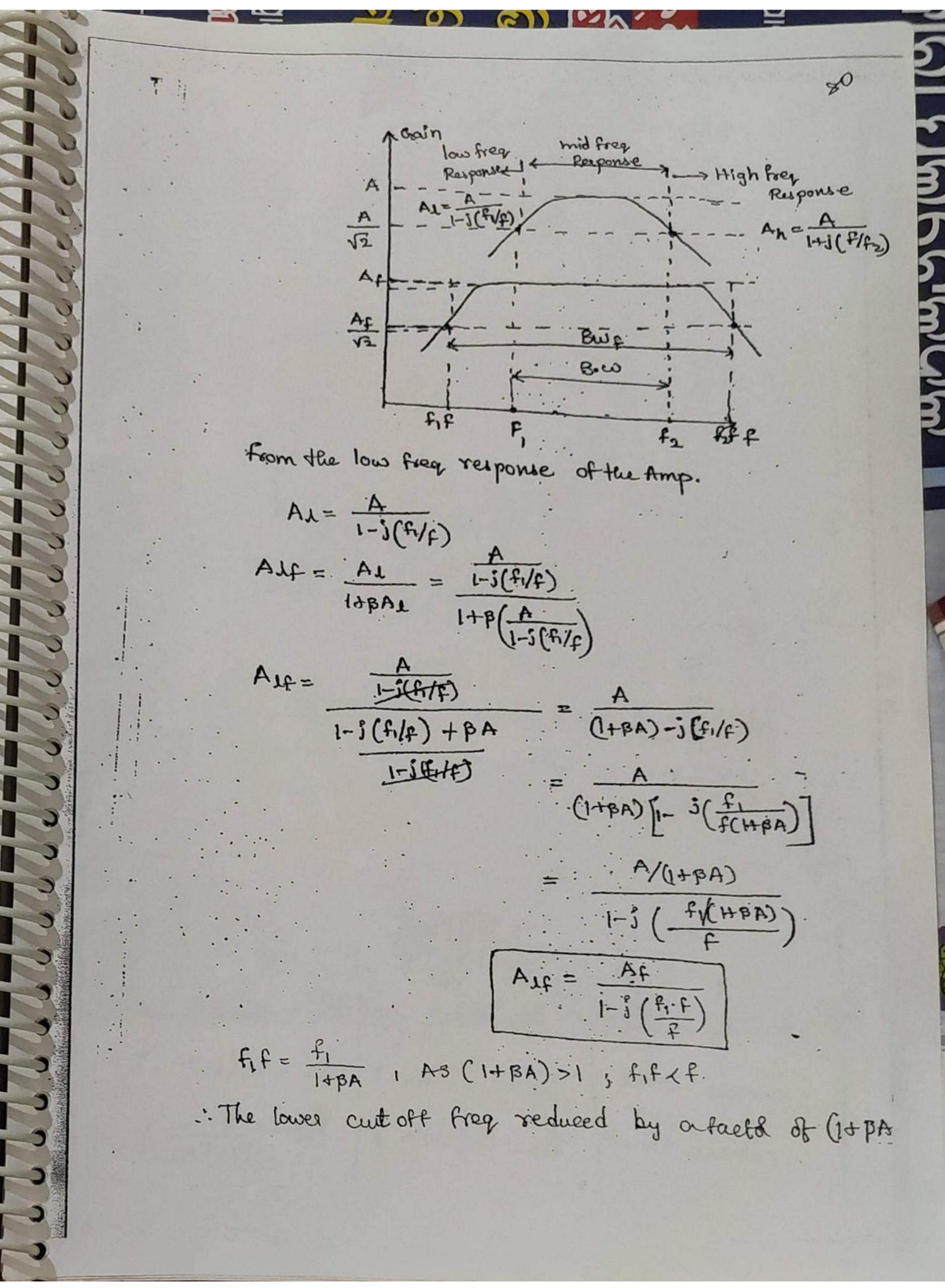

Af ~ L

Af depends only B-B'is constant. Af is also constant. As Af is independent of A' -> The N.F.B Amp thermally More Stable.

lly from high Frey response of the Amplifier, f2f = f2 (I+BA) The appear autoff freq with feedback increased by a factor of (HBA). 3. Noise Decreases:-AS BWA Norse-V Let N -> Noise of amp without feedback. " with " 4. Distoltion pecreaues: -As BW1 Distation L Let D -> Distoltion of the amp without flB. with 5. 1/2 & ofp resistances changes oppreciably:-Let R; is is Resistance of the amp without feedback. Ro -> 0/9 with Rif 7 1/P. Rof -> Olp · ilp Resistance of Resistance N. F.B amp Rif = R; (1+BA)1 ROF = RO 1+BA Voltage - series Rif = Ri (I+PA) voltage - shunt Rof = Ro 1+BA. Rif= R; (1+BA) T Current - series Rof = Ro (1+BA) 1 current-shunt Rof = Ro(1+BA) 1. Rif = Ri (1+BA)

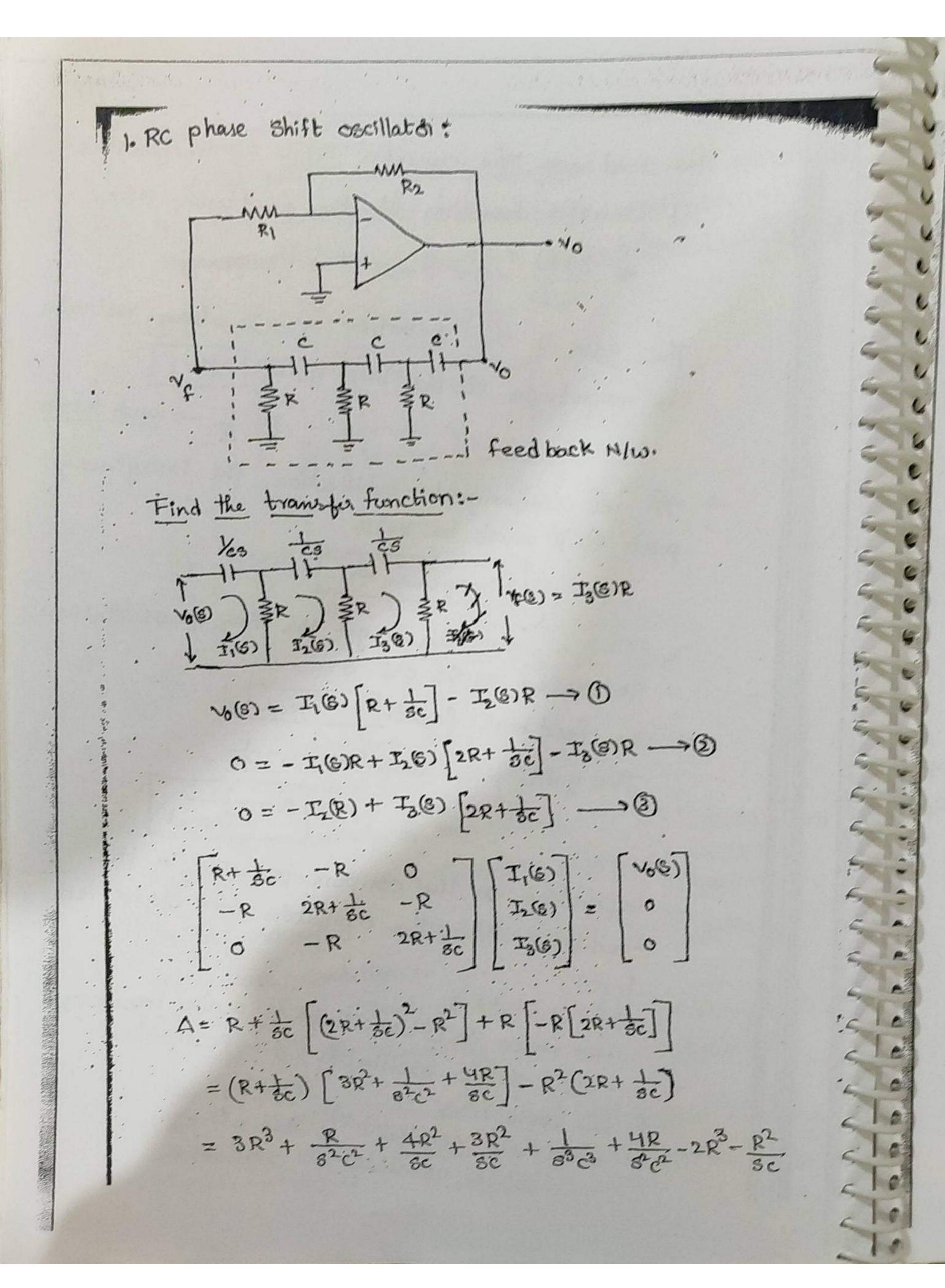

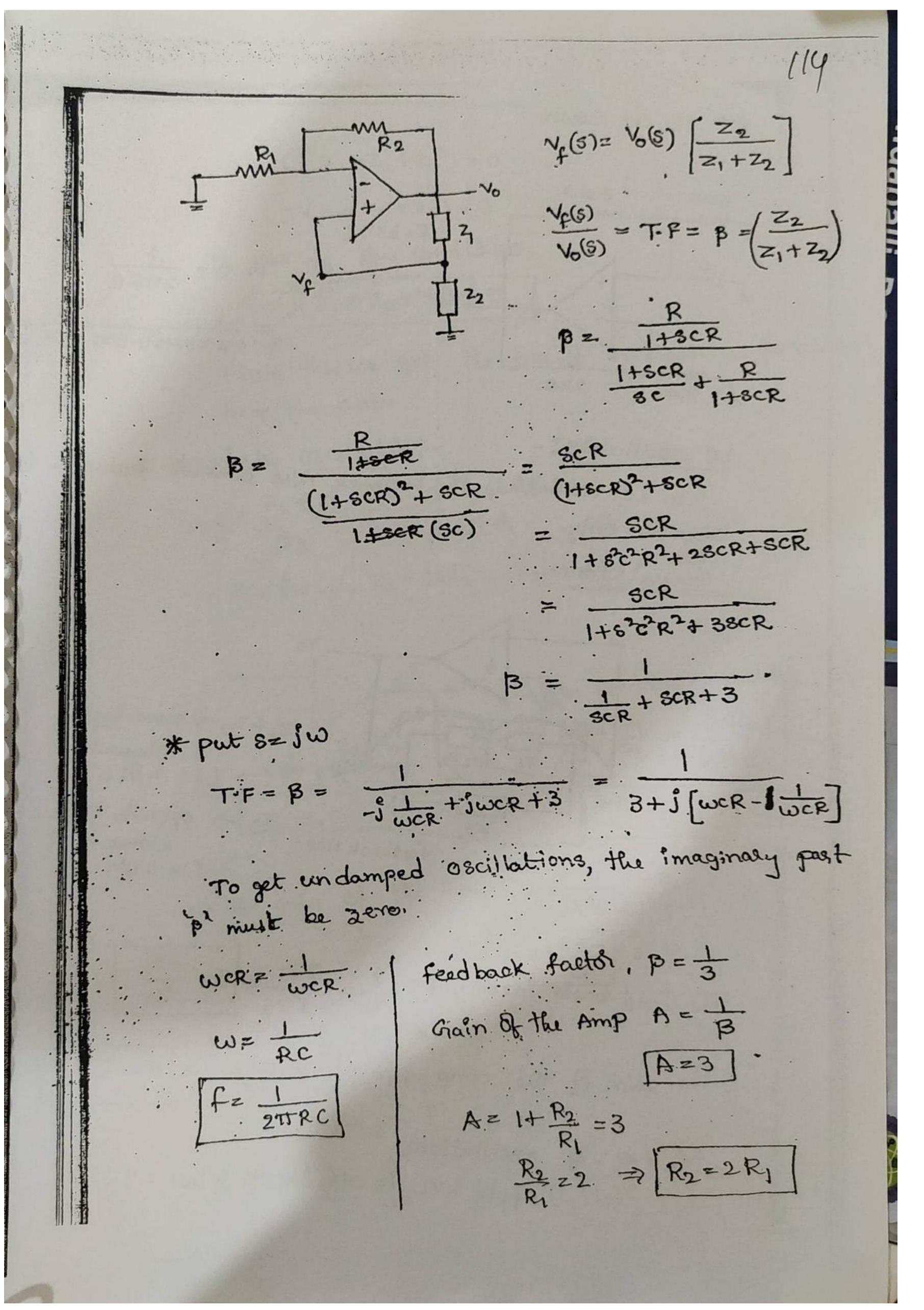

# the property of the state of th sinu soidal oscillators:-A. ckt which generates undamped sinusoidal oscillations is called sinusoidal (1) Hormonic oscillatsi. \* (undamped means Amplitude constant "periodically) feed back XO In oscillatos, Xf=X; Xo = AX9 Xr = ABX; TE = AXi > : AB=1 AB -> loop gain AB=1:=.1+50 =1100. BARKHAUSEN tis the magnetude of loop gain =1. CRITERIA ! (ii) The total phase of the loop is o'din360° conditions. To get undamped oscillations the ckt must satisfy the above conditions. > If the complifier introduces 180 of phase. [ Investing amplifier cramplifier. The remaining 1800 must introduced by the feedback. -> If the amplifier introduces of phase [Non-investing for Amplifier, CE-CE cascaded Amplifier The feedback N/w. must introduce of ohase.

-> The Feed back N/w consists RILIC -> in oscillates The transfer function of the feed back Nhw.

=> XFE) = B= Breal ± j Bimagnony.

The gain of the amplifier. A -> is alway real value The magnitude of the loop gain, [AB=1]

·· B= 1 -> must be re

-> To get undamped oscillation, the imaginary post of B must be zero.

> Bimaginary = 0

from this we get the freq of oscillation:

generated by the ckt.

> The feed back factor [B= Break].

The gain of the amplifier A= B

Breat

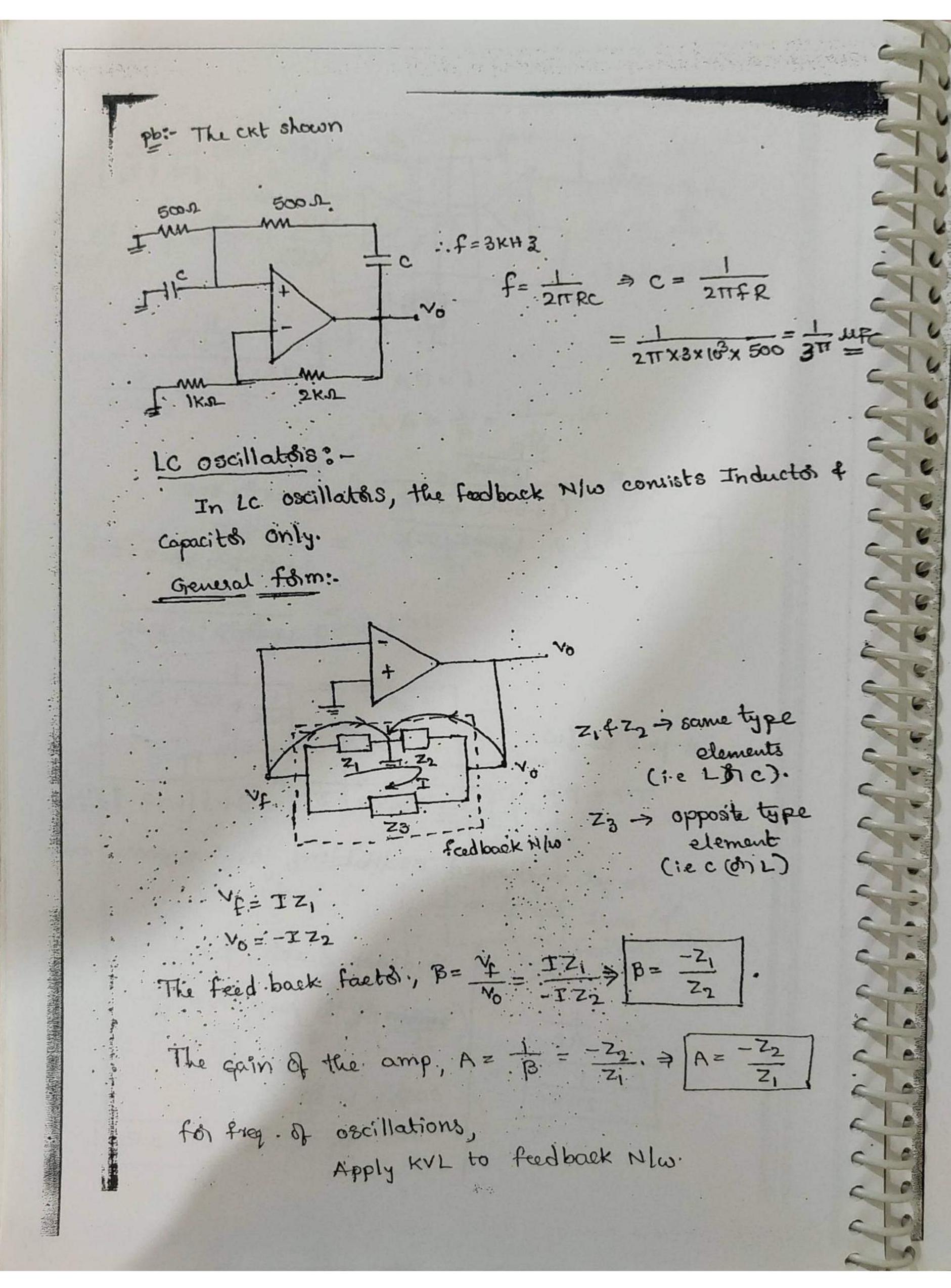

-> Depending on the components used in the feed back N/w, the oscillators are classified into:

1. RC Oscillators

- Re phase shift oscillater?

Audio frequency Oscillators.

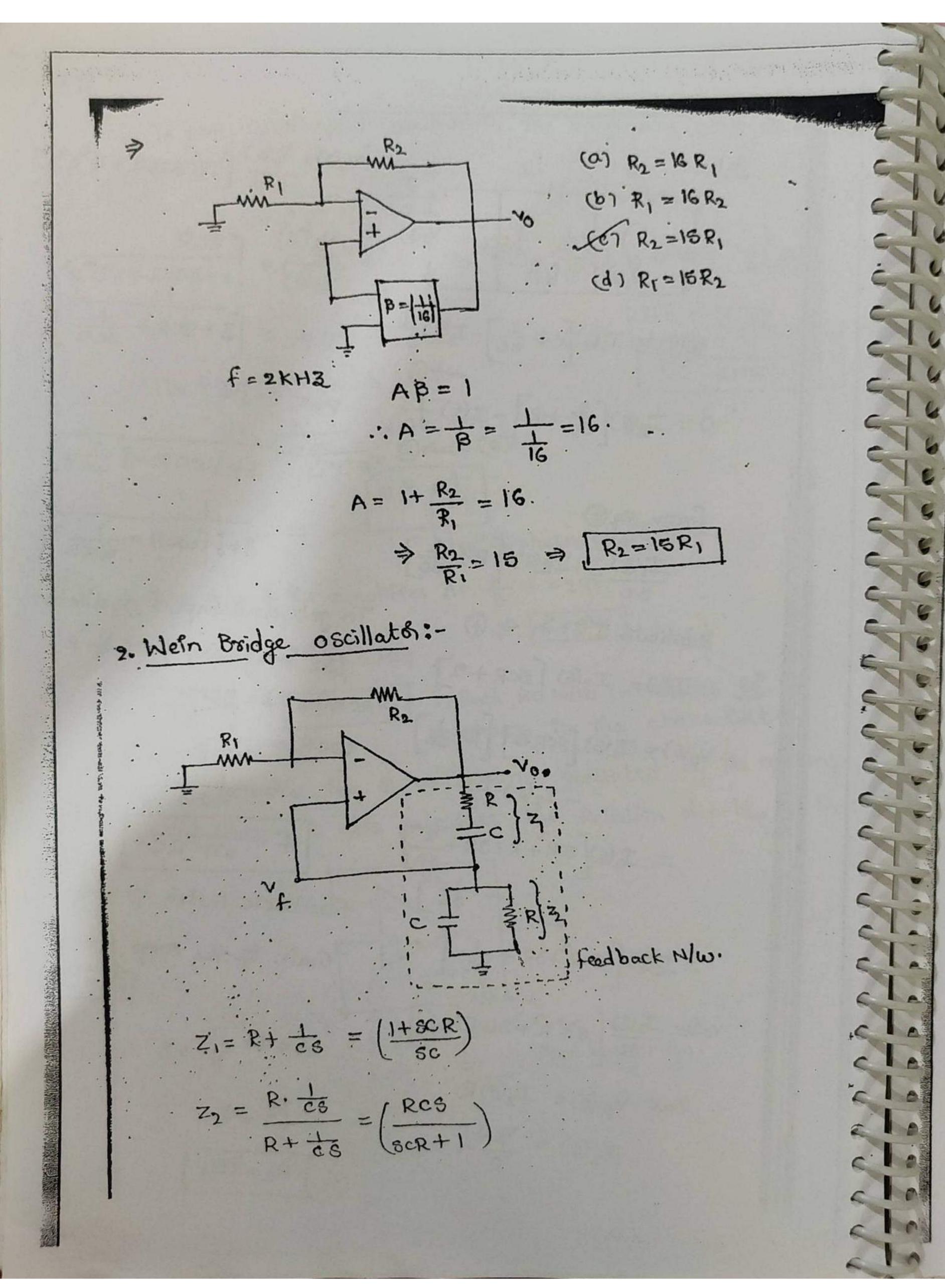

- Wein Bridge Oscillator.

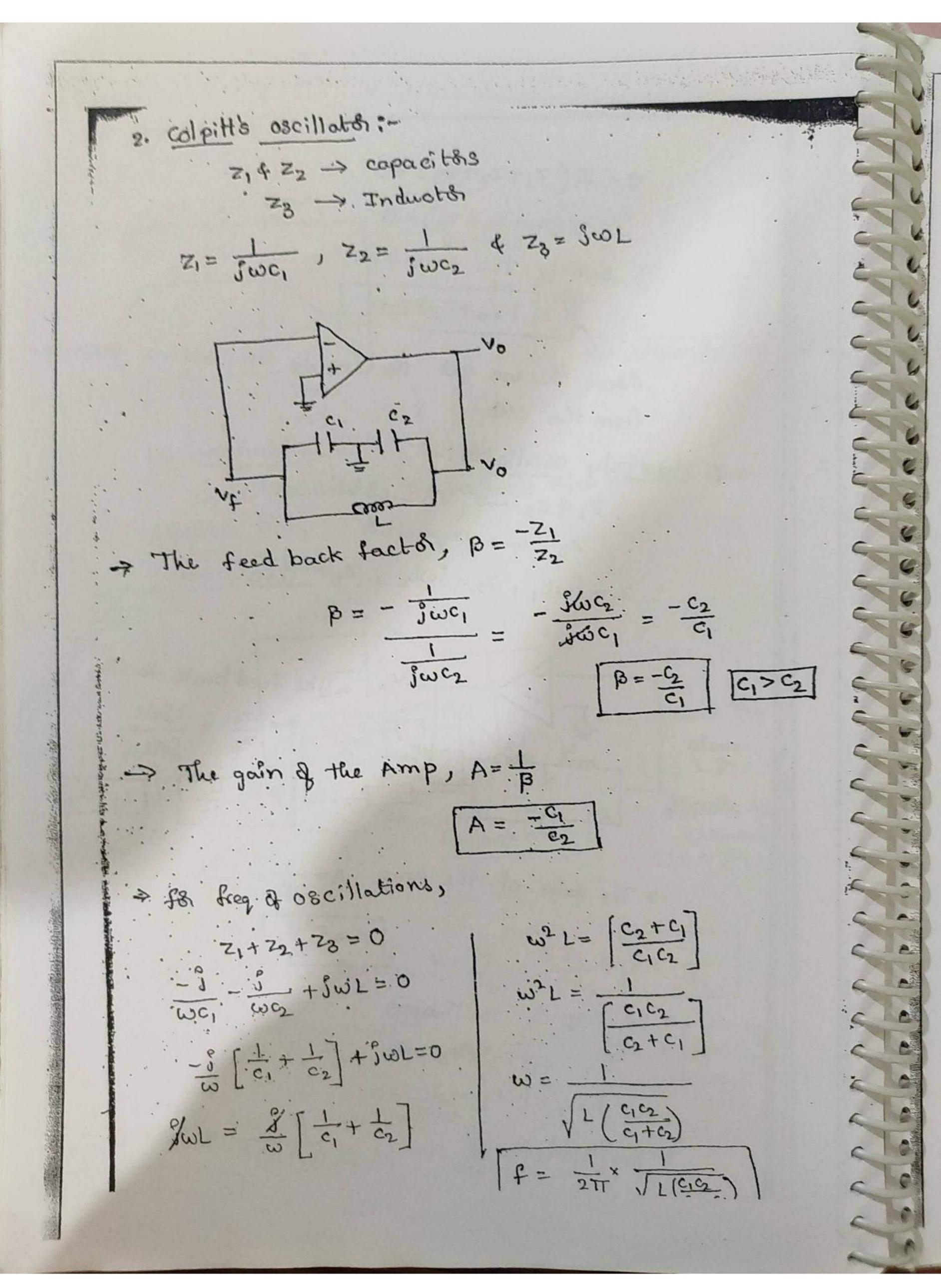

2. Le oscillators

- Hartely oscillator. Radio freq oscillatos. colpitt's oscillatos)

To get undamped oscillations, the imaginary part of B masor be zero. 271 = RCV6 The feed back factor is 1-5(6) 180° of phase blu vo & Vf. .: Each Rc N/w introduces 60° of R2 = 29R1 phase en the above ckt. 1. calculate the freez of oscillations generated by the op-amp . Okt shown & also calculate the Relation Ship blu R18 R2. feed back N/w.

$$V_{0}(S) = \frac{V_{1}(S)}{SCR} \left[ 1 + 3SCR + S^{2}c^{2}R^{2} \right]$$

$$\frac{V_{2}(S)}{V_{0}(S)} = \left[ \frac{3CR}{1 + 3SCR + S^{2}c^{2}R^{2}} \right]$$

$$T.F = \left[ \frac{3 + SCR}{3 + SCR} + \frac{1}{SCR} \right]$$

$$Put S = JW$$

$$P = \frac{1}{3 + JWCR - JWCR}$$

$$= \frac{1}{3 + JWCR}$$

$$= \frac{$$

Scanned by TapScanner

Scanned by TapScanner

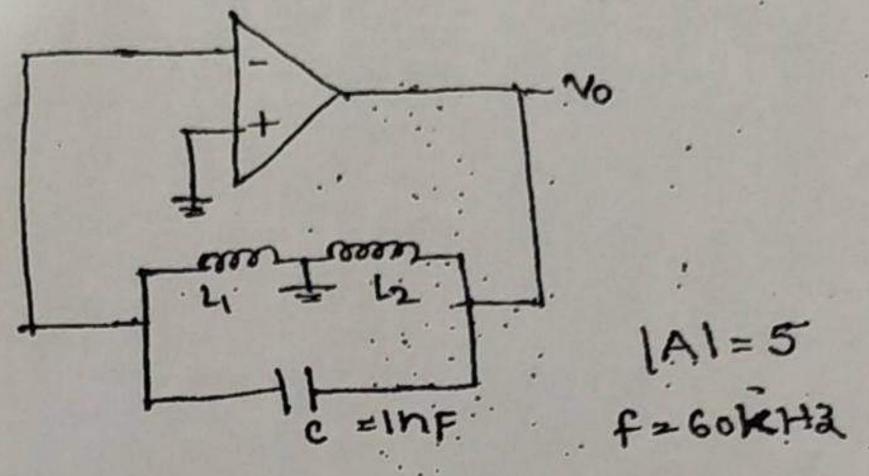

O The op-comp ckt shown is used to generate undomped oscillation of 60kHz freq calculate the required values of 4 & Lz, Assume that LAI = 5.

$$|A| = |-\frac{L_{2}}{L_{1}}| = 5$$

$$|L_{2}| = +5L_{1}$$

$$f = \frac{1}{2\pi \sqrt{(L_{1}+L_{2}).C}}$$

$$\int (L_1 + L_2)C = \frac{1}{2\pi f}$$

$$(L_1 + L_2)C = \frac{1}{4\pi^2 (60R)^2}$$

$$(L_1 + L_2) = \frac{1}{4\pi^2 (6xK)^2 \times 10^2}$$

$$= \frac{1}{4\pi^2 36 \times 10^{-1}}$$

$$L_1 + L_2 = \frac{1}{4 \cdot 03m} + \frac{1}{4 \cdot 0$$